Hoch komplizierte „smarte“ Anwendungen - Audiobearbeitung, Gesichtserkennung, Gateway etc. – benötigen also Hochleistungs-MPU-Reihen wie RZ/A und RZ/G. Besonders charmant ist dabei nicht nur die hohe Leistungsfähigkeit: Die Reihen bieten jeweils einen 2D- (RZ/A) oder 3D-Grafik-Controller (RZ/G) und -Beschleuniger, der zwei Videokanäle mit hoher Auflösung unterstützt.

Die RZ/A und RZ/G-Familien bieten die Möglichkeit, ein zusätzliches DRAM für Datenspeicher hinzuzufügen. Zudem verfügt die MPU der RZ/A1-Reihe – im Gegensatz zu Prozessoren anderer Hersteller, die ausschließlich mit externem RAM und Flash arbeiten – über einen integrierten On-Chip-Speicher von bis zu 10 MByte SRAM. Code und Daten (einschließlich grafischer Daten) können direkt aus dem großen SRAM oder über XIP dem externen QSPI-Speicher heraus ausgeführt oder gelesen werden. Bemerkenswert ist auch, dass der QSPI-Flash im DDR-Modus laufen und die Geschwindigkeit des NOR-Flashs verdoppeln kann. Die EMI-Problematik zwischen MPU und DRAM entfällt und es werden weniger Leiterplatten-Layer benötigt. Außerdem kann das beliebte QFP-Gehäuse verwendet werden. Diese Faktoren senken Produktions- und Entwicklungskosten deutlich. Angesichts des großen internen Speichers brauchen die Entwickler darüber hinaus keine weiteren Power-Management-ICs. Sollte der Kunde mehr RAM benötigen, bieten RZ/A1LC, RZ/A1L und RZ/A1lU auch eine SDRAM-Schnittstelle. Der RZ/A eignet sich daher gut für Entwicklungsingenieure, die eine leistungsstarke MPU brauchen, von einer MCU auf eine MPU umsteigen möchten und dennoch die Nachteile eines MPU-Designs vermeiden wollen.

Geballte Grafikpower

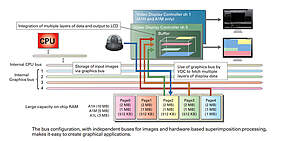

Dank der vier dezidierten internen Grafikbusse (AXI) mit je 32 Bit Breite bietet der RZ/A enorme Grafikperformance. Da der interne SRAM als Frame Buffer (mit bis zu 10,64 GB/s) genutzt werden kann, kann der Video-Controller das Bild schneller abrufen als bei einer Lösung mit externem DRAM. Der RZ/A unterstützt zwei unabhängige LCD-Displays mit einer Auflösung von 1280x800 und bis zu zwei CMOS-Kamera-Eingänge.

Mit Hilfe der über Hardware beschleunigten 2D-Vektorgrafik (OpenVG) kann eine attraktivere grafische Benutzeroberfläche erstellt werden, die bei Vergrößerung des Bildes nicht verzerrt wird. Dabei wird die Verarbeitung vom Kern zur GPU (Graphic Processing Unit) ausgelagert, so dass der MPU-Kern wichtigere Algorithmen ausführen kann. OpenVG eignet sich gut zum Beschleunigen von Flash-Speichern und skalierbaren Vektorgrafiken.

Abbildung 1: Die Bus-Konfiguration mit unabhängigen Bussen für die Bild- und hardwarebasierte Überlagerungsverarbeitung macht es einfach, grafische Anwendungen zu erstellen.

Wenn man eine Applikation plant, die bestimmte Grafikeigenschaften benötigt, bietet Renesas drei verschiedene Tools zur Auswahl: DISPLAY IT!, STREAM IT! und das GENMAI-CPU-Board. Hardware-Referenz-Designs (Pläne und Layout) sowie Demos stehen ebenfalls zur Verfügung.

Software – einfach, komfortabel, leistungsfähig

Der RZ/A ist ein einfach anzuwendendes MPU-Produkt für Entwickler, die eine hohe Leistung wollen, ohne sich vollumfängliche, detailtiefe Linux-Kenntnisse aneignen zu müssen. Dank des Renesas-Ökosystems und der entsprechenden Community kann der Entwickler sich stärker auf die Anwendungsebene konzentrieren. Auf dem RZ/A können zwei Arten von Betriebssystemen laufen: RTOS oder Embedded Linux.

Bei RTOS stehen den Kunden vier Arten von Entwicklungsumgebungen zur Verfügung: Renesas e²Studio, IAR, ARM DS-5 und Green Hills Multi.

Abbildung 2: Vier verfügbare IDEs, Compiler und Debugger.

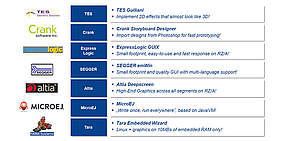

Die Software-Stacks mit Dateisystem, USB-Stack und Netzwerk-Stack für das jeweilige RTOS können von Express Logic, Segger und Micrium ausgewählt werden. Viele verschiedene GUI-Frameworks von Drittanbietern - Tes Guiliani (basiert auf FreeRTOS, kostenfrei, weil von Renesas lizenziert), Crank, Segger, Tara, Altia und Draupner - können die Entwicklung ebenfalls beschleunigen. Tes Guiliani ist für hoch qualifizierte GUI- Anwendungen geeignet und die 2D-Effekte erreichen optisch nahezu 3D-Niveau. Die Massenproduktionslizenz für Tes Guiliani basiert ebenfalls auf der Lizenz für FreeRTOS und ist somit gleichermaßen kostenfrei.

Kasten: Rutronik bietet eine Systemlösung mit RZ/A1H und Tianma-TFT-Bildschirm mit Segger emWin an. Das Kit ist ab Lager sofort verfügbar.

Abbildung 3: Verfügbare GUI-Frameworks für RZ/A.

Wie bei der Entwicklung mit dem herkömmlichen Embedded-Linux kann der Entwickler LTS Ubuntu Linux als Host verwenden. Renesas bietet einen BSP Porting Guide und ein Tool, das bei der Erstellung des BSP behilflich ist, wenn der Kunde eine eigene Platine entwickelt. Auf der Plattform GitHub steht außerdem uboot zur Verfügung, um zunächst einen gewissen Teil der Platine zu konfigurieren und Linux zu starten. Mit Hilfe von buildroot können Cross-Compilation-Toolchain, Bootloader, Kernel und Image des Root-Dateisystems erstellt werden. Anwendung, Verständnis und Änderungen werden dadurch wesentlich einfacher. Dafür stehen auf GitHub zwei verschiedene Linux-Images (Linux 4.9 und 4.14) zur Verfügung.

Keine Leistung ohne Speicher

Leistungsfähigkeit alleine genügt jedoch nicht – ohne Programmspeicher geht auch bei RZ/A und RZ/G nichts. Um den fehlenden Programmspeicher eines Mikroprozessors abzudecken, wird also zusätzlich externer Flash benötigt. Da Visualisierungs-Anwendungen in der Regel hohe Speicherkapazitäten benötigen, reicht NOR-Flash oftmals nicht aus. Entwickler müssen auf NAND-Flash-Speicher zurückgreifen. Diese stehen in verschiedenen Varianten zur Verfügung - welche die richtige Wahl ist, hängt von den Anforderungen der Applikation ab.

SLC, MLC oder TLC?

Nach dem Aufbau der Technologie unterscheidet man SLC- (Single-level-cell), MLC- (Multi-level-cell) und TLC- (Triple-level-cell) Flash. Die SLC-Technologie speichert ein Bit pro Zelle. Das bedeutet, im Floating Gate gibt es lediglich zwei verschiedene Spannungsniveaus. Dadurch sind SLC-Flash-Speicher am zuverlässigsten, aber auch am teuersten.

Die MLC-Technologie, die zwei Bit pro Zelle speichert, muss bereits vier Spannungsniveaus im Floating Gate darstellen, die TLC-Technologie bringt es auf drei Bit pro Zelle und acht Spannungsniveaus. Wichtig ist hierbei die Betrachtung der Prozesstechnologie. Viele Hersteller setzen auf immer weitere Die-Shrinks, um den Wafer-Output zu erhöhen. Je kleiner die Prozesstechnologie (aktuell liegen wir bei 15nm NAND-Flash), je geringer wird auch die Anzahl der Elektronen in einem Bit. Durch Einflüsse wie Zeit, EMV (Elektromagnetische Verträglichkeit) und Temperatur gehen jedoch Elektronen verloren. Aufgrund dieser fallenden Anzahl der Elektronen - verbunden mit der steigenden Anzahl an Spannungsniveaus - steigt die Anfälligkeit von Bit Flips, also einer unbeabsichtigten Veränderung eines Bits. TLC-Flash-Speicher sind damit sowohl die günstigste als auch die unzuverlässigste Variante.

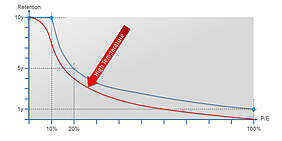

Abbildung 4: Übersteht ein SLC-Flash-Speicher rund 100.000 Schreib/Lösch-Zyklen, kommt ein MLC-Speicher noch auf 3.000, ein TLC-Speicher gerade einmal auf 500 Schreib/Lösch-Zyklen. 1 PE Cycle wird erst erreicht, sobald die komplette Density, also Kapazität, des Speichers einmal beschrieben wurde.

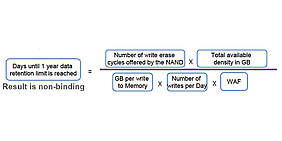

Die Anzahl der möglichen Schreib/Lösch-Zyklen (PE Cycles), die so genannte Endurance Rate, nimmt mit steigernder Bitzahl pro Zelle ab. In der Regel weicht die tatsächliche Anzahl der geschriebenen Daten von den gesendeten Daten des Mikroprozessors ab. Aufgrund der Systemoptimierung des Flashs werden z.B. 4kByte gesendete Daten mehrfach innerhalb des NAND geschrieben. Um besser einschätzen zu können, mit welcher Effektivität die Daten vom Host auf das Memory übertragen werden, kann mithilfe des WAF die Anzahl der Daten beziffert werden.

Der WAF hat damit auch eine negative Auswirkung auf die Endurance, da unter Umständen deutlich mehr geschrieben wurde als tatsächlich Daten gespeichert wurden. Dieser Faktor geht dadurch sowohl mit dem Wear Levelling als auch mit der Garbage Collection einher.

Abb. 5: Das Ergebnis ist unverbindlich.

Das sogenannte Wear Levelling sorgt dafür, dass jede Speicherzelle gleichermaßen oft genutzt und auch wieder gelöscht wird. Die Data Retention, also die maximale Zeitspanne, in der die Daten nach dem Programmieren noch im Datenfeld abgerufen werden können, steigt damit an und verlängert die Lebenszeit eines Flash-Bausteins. Je mehr Schreib/Lösch-Zyklen bei einer Anwendung anfallen oder je höher die durchschnittliche Betriebstemperatur ist, desto eher sollte zu MLC oder gar SLC Flash-Speicher gegriffen werden, um eine ausreichende Lebensdauer des Bausteins gewährleisten zu können.

Ein wichtiges Instrument zur Sicherung der Langlebigkeit von Speichern ist der ECC - ein Fehlerkorrekturverfahren, das beim Auslesen des Speichers alle Bits mit der Checksumme vergleicht und so fehlerhafte Zellen identifiziert und korrigiert. Die Menge der diktierbaren Fehler hängt von der Größe des ECC ab (z.B. 8bit). Wird die Funktion vom Host übernommen, ist es unerlässlich, die Kompatibilität zwischen Memory und Prozessor zu prüfen.

Gerade ältere Prozessoren haben eine integrierte ECC, die neuere Speichermodelle nicht mehr unterstützen. Um diese Kunden jedoch auch zukünftig unterstützen zu können, hat Rutronik mit INSIGNIS und Alliance Memory zwei Speicherhersteller, die ältere und damit kompatible Derivate anbieten. Bei der Nutzung von Toshiba Flash kann alternativ auch auf BENAND™ zurückgegriffen werden. Dieser SLC NAND hat bereits einen integrierten ECC, der die Fehlerkorrektur direkt im Speicher übernimmt und der Host keinerlei Einfluss darauf nehmen muss.

Verfügt der Mikroprozessor nicht über eine NAND-Schnittstelle (wie im Falle des RZ/A1L), kann herkömmliches NOR Flash eingesetzt oder auf Serial-NAND zurückgegriffen werden. Diese Speicher besitzen ein SPI-Interface, das bei Mikrocontrollern und -prozessoren standardmäßig integriert ist. Eine andere Variante sind bereits gemanagte NAND-Speicher. Für das Management sorgt eine im Speicher integrierte Steuereinheit. Die sogenannten e·MMC (embedded Multi Media Card) sind meist in MLC- Technologie gefertigt. Auch Funktionen wie das Bad Block Management, Wear Levelling und Garbage Collection sind bereits im Speicher enthalten und müssen nicht vom Host, also dem Mikroprozessor, übernommen werden.

Arbeitsspeicher für alle Bedarfe

Reicht das bereits im Host integrierte RAM nicht aus, kann es ebenfalls durch einen externen Speicher ergänzt werden. Bei den RZ/A-Prozessoren steht hier internes RAM zwischen 3 und 10MByte zur Verfügung. Die RZ/G-Serie kann mit externem RAM erweitert werden. Für externen RAM stehen die flüchtigen Speichertypen SRAM (statisches RAM) und SDRAM (dynamisches RAM) zur Auswahl. SRAM bietet einen schnellen Zugriff und kann gespeicherte Daten bis zu einigen Jahren erhalten. Allerdings verfügen SRAM nur über kleine Datenkapazitäten, benötigen viel Platz auf dem PCB und sind im Vergleich zu DRAM deutlich teurer. DRAM bietet zwar nur mittlere Zugriffszeiten und benötigt für den Datenerhalt eine zyklische Auffrischung, doch es punktet mit hoher Datendichte auf kleiner Oberfläche und günstigem Preis.

SDRAM steht wiederum als SDR- (Single Data Rate) und DDR- (Double Data Rate) Modell zur Wahl. Im Vergleich zu SDR- können DDR-Speicher die doppelte Datenrate übertragen, da sie die an- und absteigende Taktflanke des Datensignals zur Übertragung nutzen. Um die relativ langsame Zugriffszeit des SDRAM zu verkürzen, wird das Prefetching eingesetzt. Dabei greift der DDR-Speicher parallel auf mehrere Speicherzellen zu. Die in einen Puffer geschriebenen Daten werden anschließend mit der höheren externen Datenrate des Hosts ausgegeben. Arbeitet die ursprüngliche DDR-Technologie mit zweifachem Prefetching, kommt bei DDR2 vierfaches, bei DDR3 und DDR4 achtfaches Prefetching zum Einsatz.

Beide Speicherformen haben sowohl Vor- als auch Nachteile. Eine Kombination aller Vorteile erscheint zwar unrealistisch, ist aber durch FRAM tatsächlich möglich. FRAM (Ferroelectric Random Access Memory) kombiniert durch seine spezielle Technologie drei wichtige Vorteile: es ist schnell (150ns Zugriffszeit), hat einen sehr geringen Stromverbrauch und eine deutliche längere Lebenszeit als Flash oder SDRAM (10 Millionen Lese-/ Schreibzyklen). Hinzu kommt, dass FRAM - auch wenn der Name etwas anderes vermuten lässt - non-volatile Speicher sind und damit auch bei Stromverlust die Daten gespeichert bleiben. Allerdings bietet Fujitsu mit seiner Speicherform nur kleine Kapazitäten - vergleichbar mit EEPROM – die vor allem bei Metering/ Energy, Point of Sales und IoT-Anwendungen die perfekte Lösung bieten können.

Bei der Wahl des richtigen Speichers kommt es daher darauf an, sich die richtigen Fragen zu stellen: Was möchte ich speichern und wie lange? Was kostet der Verlust der Daten? Welche Endurance- und Data-Retention-Rate brauche ich dafür?

Sind alle diese Fragen eindeutig beantwortet, erhält man ein passgenaues Zusammenspiel zwischen MPU und Memory.

Glossar:

Bad Block Management = Feststellung defekter Datenblöcke

Buildroot = einfaches, effizientes und einfach zu benutzendes Tool, um Embedded-Linux-Systeme zu erzeugen

BSP = Board Support Package

ECC = Error Correcting Code

Garbage Collection = automatische Speicherbereinigung

GitHub = Onlinedienst, der Software-Entwicklungsprojekte auf seinen Servern bereitstellt

GPU = Graphics Processing Unit / Grafikprozessor

PCB= Printed Circuit Board / Leiterplatte

Prefetching = Vorabruf von Speicherinhalten

RAM = Random Access Memory

uboot = ein universaler Bootloader

WAF = Write Amplification Factor

Wear Levelling = Verschleißausgleich des Speichers