# TLE4972

User manual

# Scope and purpose

This is the user manual of the product family XENSIV<sup>™</sup> TLE4972.

TLE4972 is a high precision miniature coreless magnetic current sensor for AC and DC measurements with analog interface and two fast over-current detection outputs. Infineon's well-established and robust monolithic Hall technology enables accurate and highly linear measurement of the magnetic field induced by currents flowing in an external conductor. With a full scale up to  $\pm 31$ mT it is possible to measure currents up to 2,000 ampere. All negative effects (e.g. saturation, hysteresis) commonly known from open loop sensors using flux concentration techniques are avoided.

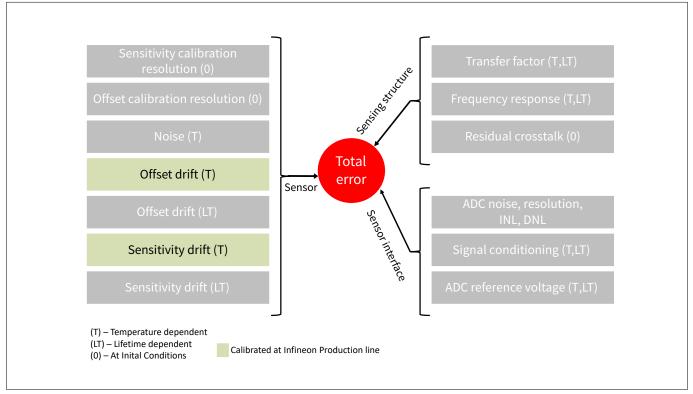

The digitally assisted analog concept of TLE4972 offers superior stability over temperature and lifetime thanks to the Infineon proprietary mechanical stress and temperature compensation. The temperature drift of sensitivity is corrected at sensor level using a 3<sup>rd</sup> order polynom. The offset drift is corrected at sensor level using a 2<sup>nd</sup> order polynom. The drift performance specified in the product datasheet [1] is verified by extensive lab characterization and derived from AEC-Q100 qualification when applicable.

The sensor is an ISO 26262 Safety Element out of Context for safety requirements up to ASIL B and is equipped with internal self-diagnostics. Detailed information are available in the Safety Manual [2].

The user manual describes the output modes and sensing principle in Chapter 1 and the detailed technical aspects of the device required for integration in a system in Chapter 2. The internal block diagram and the typical application circuit are available in the product datasheet [1].

TLE4972 features an integrated EEPROM enabling high flexibility at system level. The document provides a description of the available interface commands in Chapter 3. Measurement range, as well as OCD thresholds and output mode can be programmed by the user. The full set of programmable settings is explained in Chapter 4.2.

Initial errors due to part to part variation and misalignment with respect to the current rail can be canceled out through a single point, room temperature calibration. Details about calibration concept and error components are reported in Chapter 6.

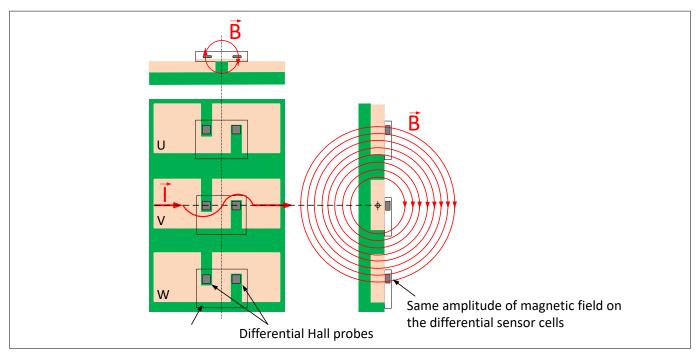

The device is intrinsically robust against stray fields thanks to the differential sensing technology, and crosstalk between nearby phases in multi-phase systems can be compensated at system level as explained in Chapter 7.

Deviation of behavior from datasheet specifications when the ratiometricity settings are re-programmed is explained in Chapter 8.2.

The devices to which this manual applies are listed in the table "related devices" below.

For the device's specification, please see the respective datasheet [1].

# **Intended** audience

This user manual is written for experienced hardware and software engineers involved in the implementation of the device into a system. It is the responsibility of the system integrator to ensure that the product is suitable for the chosen application and that the procedures described within this user manual are correctly followed.

# **Related devices**

| Name           | Ordering Code | Package    |

|----------------|---------------|------------|

| TLE4972-AE35D5 | SP004914362   | PG-TDSO-16 |

| TLE4972-AE35S5 | SP004914370   | PG-VSON-6  |

Table of contents

### **Table of contents**

|       | Table of contents   2                                         |

|-------|---------------------------------------------------------------|

| 1     | Sensing concept                                               |

| 1.1   | Sensing principle                                             |

| 1.2   | Sensitivity and transfer factor                               |

| 1.3   | Fully-differential output mode5                               |

| 1.4   | Semi-differential output mode                                 |

| 1.5   | Single-ended output mode6                                     |

| 2     | System integration                                            |

| 2.1   | 3.3 V domain integration                                      |

| 2.1.1 | Application circuit in fully-differential output mode (3.3 V) |

| 2.1.2 | Application circuit in semi-differential output mode (3.3 V)  |

| 2.1.3 | Application circuit in single-ended output mode (3.3 V)       |

| 2.1.4 | Application circuit for in-system programming (3.3 V)         |

| 2.2   | 5 V domain integration                                        |

| 2.2.1 | Converting from 5 V to 3.3 V                                  |

| 2.2.2 | Interfacing AOUT and VREF to the microcontroller              |

| 2.2.3 | Application circuit in fully-differential output mode (5 V)   |

| 2.2.4 | Application circuit in semi-differential output mode (5 V)    |

| 2.2.5 | Application circuit in single-ended output mode (5 V)         |

| 2.2.6 | Application circuit for in-system programming (5 V)           |

| 3     | Serial Inspection and Configuration Interface (SICI)          |

| 3.1   | SICI hardware layer and voltage ratings 15                    |

| 3.2   | Internal State Machine (ISM)                                  |

| 3.3   | SICI timing specifications                                    |

| 3.4   | SICI activation                                               |

| 3.5   | SICI standard commands                                        |

| 3.6   | Internal temperature readout example                          |

| 4     | Internal registers and EEPROM content                         |

| 4.1   | Internal registers                                            |

| 4.2   | EEPROM content                                                |

| 5     | EEPROM programming                                            |

| 5.1   | EEPROM CRC calculation                                        |

| 5.2   | EEPROM CRC calculation example                                |

| 5.3   | EEPROM programming example 32                                 |

| 6     | Calibration                                                   |

| 6.1   | Sensitivity and offset measurement35                          |

| 6.2   | Transfer factor estimation                                    |

| 6.3   | Desired sensitivity                                           |

### Table of contents

| 6.4     | Target sensitivity                                 |

|---------|----------------------------------------------------|

| 6.5     | Sensor level calibration                           |

| 6.5.1   | Calibration concept                                |

| 6.5.2   | Double code word calibration                       |

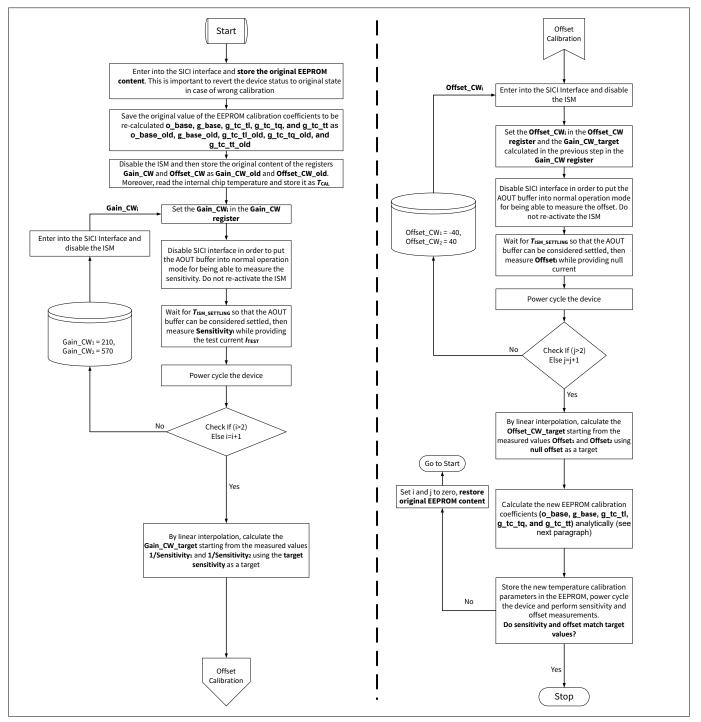

| 6.5.2.1 | Double Code Word method procedure 40               |

| 6.5.2.2 | Calculation of new EEPROM calibration coefficients |

| 6.6     | OCD threshold calibration                          |

| 7       | Stray fields and crosstalk                         |

| 7.1     | Differential measurement principle                 |

| 7.2     | Intrinsic crosstalk compensation 44                |

| 7.3     | Crosstalk compensation matrix46                    |

| 8       | Non default configuration                          |

| 8.1     | TLE4972 non-default configuration                  |

| 8.2     | Ratiometricity OFF/ON setting48                    |

| 9       | <b>Glossary</b>                                    |

| 10      | <b>References</b>                                  |

| 11      | Revision History                                   |

|         | <b>Disclaimer</b>                                  |

**1** Sensing concept

### **1** Sensing concept

In this chapter the signal naming convention is explained. In addition, the output modes in which the sensor can be configured are described in the following sections. The detailed formulas for each output mode are reported in the product datasheet [1].

### 1.1 Sensing principle

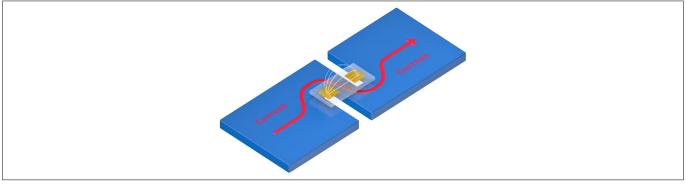

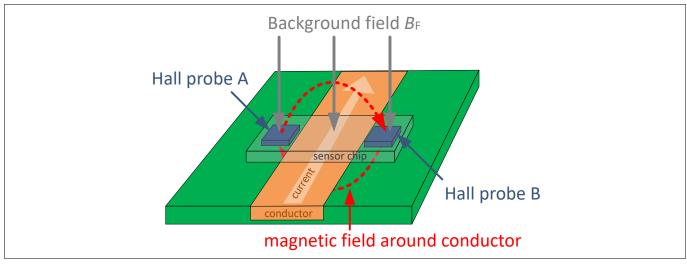

In the figure below the sensor die is shown together with a sensing structure example realized on a conductor. The sensor features two Hall based sensing elements, or probes, enabling a differential sensing principle. The Hall probes are sensitive to the component of the magnetic field orthogonal to the conductor. The magnetic field lines are generated so that the orthogonal component of the magnetic field has opposite directions on the two sensing elements.

Figure 1 Magnetic field on sensing elements with core-less differential current sensor

$B_{\text{DIFF}}$  is the average differential magnetic field at the Hall probes location, respectively  $B_{\text{H1}}$  and  $B_{\text{H2}}$ :

$$B_{DIFF} = \frac{B_{H1} - B_{H2}}{2}$$

(1)

### 1.2 Sensitivity and transfer factor

The sensor features an analog output, which is used to provide the information of the measured current. The analog measurement result is available as the differential output voltage  $V_0$ .

Being  $S_X$  the sensitivity in [mV/mT] and  $V_{OQ}$  the quiescent voltage of the sensor in [V], in all output modes except fully-differential, the differential output voltage  $V_O$  can be expressed as:

$$V_O = V(AOUT) - V(VREF) = S_X \times B_{DIFF}$$

<sup>(2)</sup>

In fully-differential mode, the differential output voltage  $V_0$  can be expressed as:

$$V_O = V(AOUT) - V(VREF) = 2 \times S_X \times B_{DIFF}$$

(3)

*Note:* The sensor features a ratiometric output mode. Parts without ratiometricity cannot be reprogrammed in order to enable it and vice versa. Please check with your local sales representative whether ratiometric parts are available.

#### 1 Sensing concept

The sensitivity *S*, whose dimension is [V/A], is defined as:

$$S = S_X \times TF \tag{4}$$

where  $S_X$  is the sensitivity in [mV/mT] linked to the measurement range programmed in the EEPROM and *TF* is the current rail transfer factor in [T/A] associated to the sensing structure, defined as  $B_{\text{DIFF}}$  [T] divided by I [A]. The configurable values for  $S_X$  ( $S_X=S_1,...,S_6$ ) are reported in the product datasheet [1].

The current rail transfer factor *TF* indicates the magnetic coupling between sensor and sensing structure. This value is usually expressed as its nominal value for a DC current, when the sensor is in the nominal position with respect to the current rail.

It will be directly influenced by:

- Displacement of sensor in the 3 directions of space, due to e.g. soldering tolerances, mechanical vibrations or material expansion/contraction over temperature and lifetime;

- Manufacturing tolerances of bus-bars and PCB traces;

- Skin effect and eddy current effect in the conductor, when an AC current flows through it;

- Presence of magnetic parts in the system, or of heatsinks/conductor nearby the sensor; eddy currents can be induced in any conductor, also on an aluminum heatsink, and they can hence influence the frequency response of the current measurement system.

Further details about desired sensitivity and target sensitivity for calibration are reported in Chapter 6.

### 1.3 Fully-differential output mode

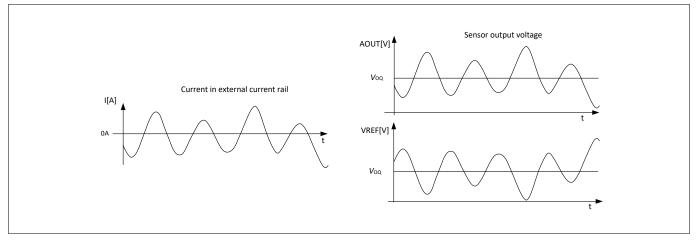

Sensor output for fully-differential mode

1 Sensing concept

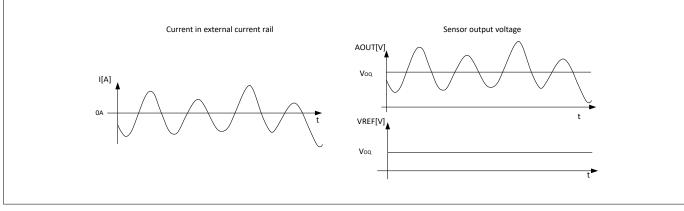

### 1.4 Semi-differential output mode

### Sensor output for semi-differential mode

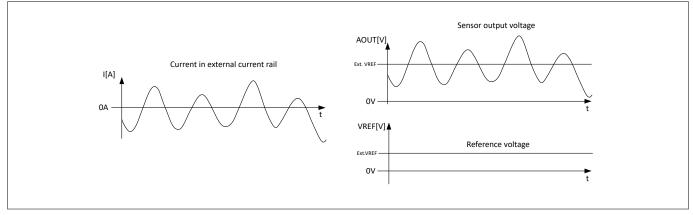

# 1.5 Single-ended output mode

Figure 4

Sensor output for single-ended mode

# 2 System integration

The sensor works with 3.3 V typical voltage power supply to follow the trend of reduced power supply voltage. However, it can also fit in 5 V systems. This chapter explains how the sensor shall be connected to both 3.3 V and 5 V systems.

### 2.1 3.3 V domain integration

This section describes how to connect the sensor to the microcontroller in a 3.3 V system in the different operating modes.

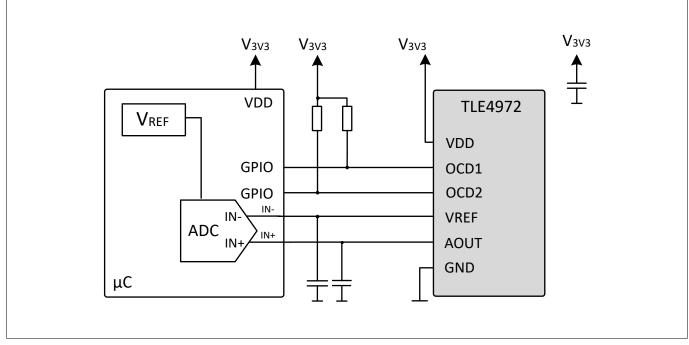

### 2.1.1 Application circuit in fully-differential output mode (3.3 V)

The following figure shows a sketch of application diagram in fully-differential mode. For the detailed application circuit please refer to the product datasheet [1].

Figure 5

Application circuit in fully-differential mode

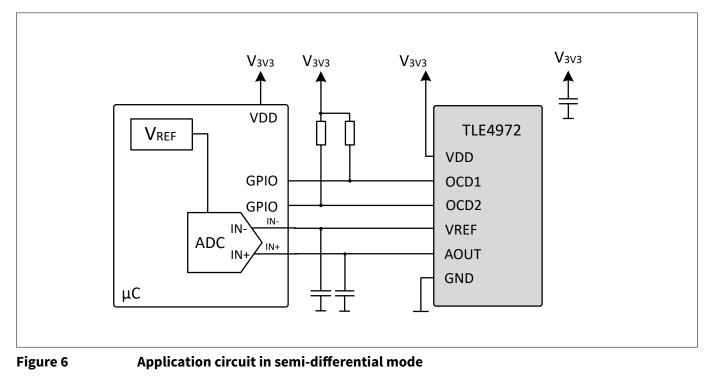

### 2.1.2 Application circuit in semi-differential output mode (3.3 V)

The following figure shows a sketch of application diagram in semi-differential mode. For the detailed application circuit please refer to the product datasheet [1].

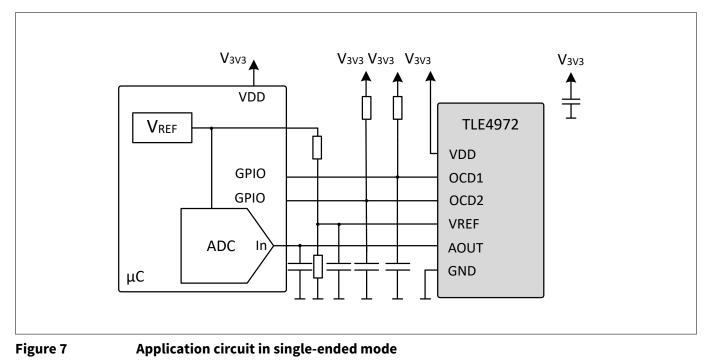

### 2.1.3 Application circuit in single-ended output mode (3.3 V)

The following figure shows a sketch of application diagram in single-ended mode. A resistive divider circuit is used to supply the reference voltage externally, when the VREF is derived from the ADC or  $\mu$ C reference voltage. For the detailed application circuit please refer to the product datasheet [1].

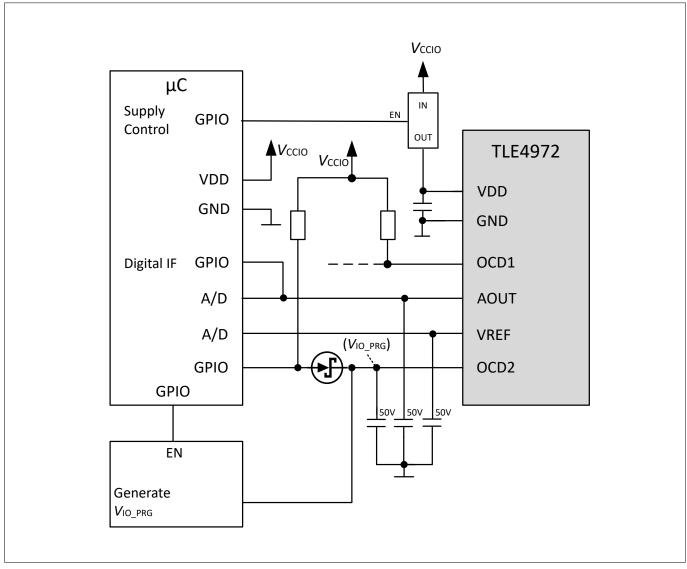

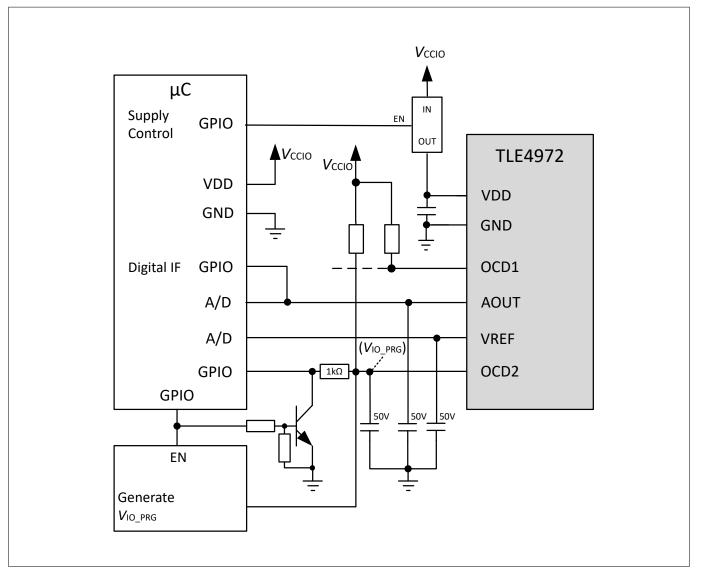

### 2.1.4 Application circuit for in-system programming (3.3 V)

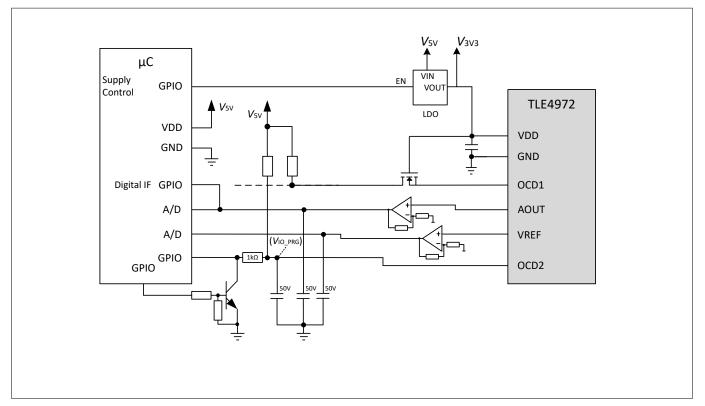

In case in-system programming is needed, the figure below shows the typical application circuit that enables in-system programming from microcontroller side in 3.3 V systems. In case an external programmer is used, in-system  $V_{IO}$  programmer is not needed. Please refer to Chapter 3.1 for further details.

SICI Application circuit with Schottky diode

#### 2 System integration

#### Figure 9 SICI Application circuit with pull-down transistor

Note: In order to protect the  $\mu$ C and other ICs connected to the OCD2 line a hardware protection scheme must be implemented. In the figure above the OCD2 line at microcontroller side is protected through a Schottky diode. This solution is simple, but doesn 't allow a fast pull-down of the OCD2 line from microcontroller side, that is needed for the diagnosis mode activation. Details about the diagnosis mode are provided in the Safety Manual [2]. An alternative is shown in the second proposed application circuit, where the OCD2 line at microcontroller side is pulled down through a 1 k $\Omega$  resistor. This solution allows a fast diagnosis mode activation from microcontroller.

Protecting the microcontroller from the programming voltage on OCD2 pin is not needed in case that the sensors lie on a separate PCB which is not connected to the system during programming phase.

Note: In order to allow in-system programming with an external programmer, the sensor pins VDD, GND, AOUT and OCD2 must be routed to the external programmer with a dedicated on-board connector. For end of line in-system calibration, also VREF must be routed to the external programmer in order to read the differential output voltage needed by the calibration routine.

*Note:* Do not connect OCD2 pins from different sensors together, if diagnosis mode is enabled in the EEPROM (default). If all OCD2s are tied together, the OCD2 fault indication of one sensor might unintentionally

activate the diagnosis mode on the other sensors by forcing the pin to ground. Details about the diagnosis mode are provided in the Safety Manual [2].

### 2.2 5 V domain integration

This chapter discusses a proposal to connect TLE4972 sensor with a 5 V microcontroller.

### 2.2.1 Converting from 5 V to 3.3 V

If the supply of the control system is 5 V and not 3.3 V, a step-down of the supply voltage is needed.

The simplest way to generate a 3.3 V supply from a 5 V supply is by using a resistive voltage divider. However, when using a resistive voltage divider one has to consider the following drawbacks:

- resistors have tolerances, hence in series-production the generated output supply may differ from the initially calculated value;

- the current flowing from the upper resistor to the sensor dissipates power. Please refer to product datasheet [1] for typical and maximum current consumption;

- the generated voltage is dependent on the current consumption of the sensor, hence it is not stable and may be subjected to variations.

Additionally, in order to reduce the effect of the load current on the voltage divider output voltage, the resistor cannot be too large. On the other hand, by using low resistor values the overall current flowing through the voltage divider to ground increases, and hence the power dissipated in the resistors also increases, leading to unnecessary power dissipation.

For the reasons mentioned above it is recommended to generate the 3.3 V using a voltage regulator. Indeed, the power dissipated in the voltage regulator is lower and the voltage is more stable since usually a control loop is implemented, including also active devices (e.g. BJT, MOSFET). Suitable devices could be Linear Voltage Regulators (LDO) from Infineon:https://www.infineon.com/cms/en/product/power/linear-voltage-regulator/

### 2.2.2 Interfacing AOUT and VREF to the microcontroller

In order to separate the 3.3 V and 5 V voltage domains and to adapt the signal dynamic from 3.3 V to 5 V, it is recommended to use operational amplifiers in non-inverting configuration.

The selected device shall have:

- Low offset to not add offset to the current sensing chain;

- Low noise to not add noise to the current sensing chain;

- Rail to rail capability to preserve the large linear range of the sensor;

- True single supply (0 5 V) to be compatible with the supply of the system;

- Good bandwidth sufficiently large to fit the application requirements.

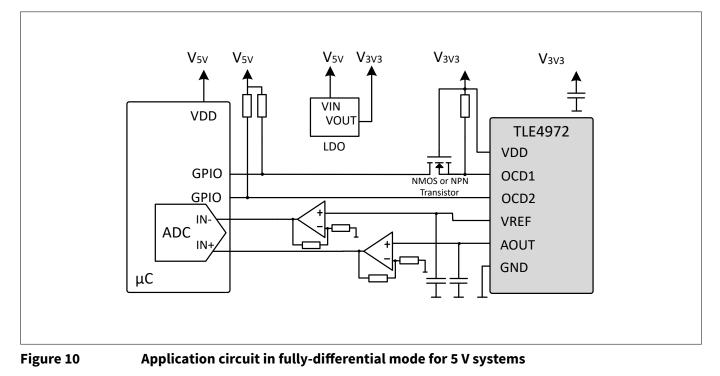

# 2.2.3 Application circuit in fully-differential output mode (5 V)

The following figure shows a sketch of application diagram in fully-differential mode in a 5 V system. For the detailed application circuit please refer to the product datasheet [1].

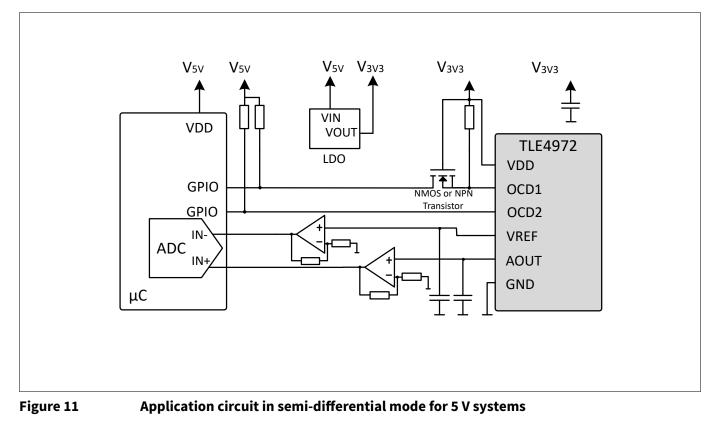

### 2.2.4 Application circuit in semi-differential output mode (5 V)

The following figure shows a sketch of application diagram in semi-differential mode in a 5 V system. For the detailed application circuit please refer to the product datasheet [1].

### 2.2.5 Application circuit in single-ended output mode (5 V)

The following figure shows a sketch of application diagram in single-ended mode in a 5 V system. For the detailed application circuit please refer to the product datasheet [1].

#### Figure 12 Application circuit in single-ended mode for 5 V systems

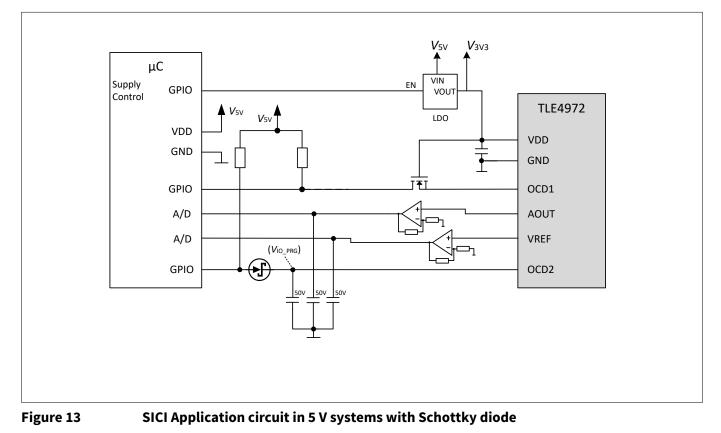

### 2.2.6 Application circuit for in-system programming (5 V)

In case of 5 V systems, programming is only possible through an external programmer connected to the 3.3 V sensor domain. Please refer to Chapter 3.1 for further details.

#### 2 System integration

#### Figure 14 SICI Application circuit in 5 V systems with pull-down transistor

Note: In order to protect the  $\mu$ C and other ICs connected to the OCD2 line a hardware protection scheme must be implemented. In the figure above the OCD2 line at microcontroller side is protected through a Schottky diode. This solution is simple, but doesn 't allow a fast pull-down of the OCD2 line from microcontroller side, that is needed for the diagnosis mode activation. Details about the diagnosis mode are provided in the Safety Manual [2]. An alternative is shown in the second proposed application circuit, where the OCD2 line at microcontroller side is pulled down through a 1 k $\Omega$  resistor. This solution allows a fast diagnosis mode activation from microcontroller.

Protecting the microcontroller from the programming voltage on OCD2 pin is not needed in case that the sensors lie on a separate PCB which is not connected to the system during programming phase.

- Note: In order to allow in-system programming with an external programmer, the sensor pins VDD, GND, AOUT and OCD2 must be routed to the external programmer with a dedicated on-board connector. For end of line in-system calibration, also VREF must be routed to the external programmer in order to read the differential output voltage needed by the calibration routine.

- Note: Do not connect OCD2 pins from different sensors together, if diagnosis mode is enabled in the EEPROM (default). If all OCD2s are tied together, the OCD2 fault indication of one sensor might unintentionally activate the diagnosis mode on the other sensors by forcing the pin to ground. Details about the diagnosis mode are provided in the Safety Manual [2].

**3 Serial Inspection and Configuration Interface (SICI)**

#### 3

Serial Inspection and Configuration Interface (SICI)

### 3.1 SICI hardware layer and voltage ratings

The sensor provides a 16 bits bidirectional one wire digital interface to access the internal EEPROM and internal registers. The application circuits for in-system programming in case of 3.3 V and 5 V systems and the needed system level precautions are described in Chapter 2.1.4 and Chapter 2.2.6. The AOUT pin is connected to a GPIO port in order to establish the communication between the sensor and the microcontroller. The communication is based on transmitting a bitstream from microcontroller to the sensor. The AOUT pin is used as an I/O pin to read and write on the SICI bus by forcing the pin to low/high with a defined timing. The EEPROM is effectively programmed by applying the  $V_{IO_{PRG}}$  voltage to the OCD2 pin.

Table 1

SICI operating parameters

| Parameter                        | Symbol                 | Min. | Тур. | Max. | Unit | Note                                               |

|----------------------------------|------------------------|------|------|------|------|----------------------------------------------------|

| Voltage level<br>for SICI – High | V <sub>SICI_HIGH</sub> | 1.6  | 3.3  | -    | V    | High state<br>(transition<br>from low to<br>high). |

| Voltage level<br>for SICI – Low  | V <sub>SICI_LOW</sub>  | -    | 0    | 1.3  | V    | Low state<br>(transition<br>from high to<br>low).  |

# 3.2 Internal State Machine (ISM)

The TLE4972 features a digital signal conditioning concept. The Internal State Machine (ISM) optimizes in real time the output stage performance, providing stable sensor behavior over temperature and lifetime. The ISM has to be disabled during programming, in order to avoid write conflicts to internal registers. The reactivation of the ISM happens through power cycle of the device, or by setting the corresponding bit in the internal bitmap. Please refer to Chapter 4.1.

### 3.3 SICI timing specifications

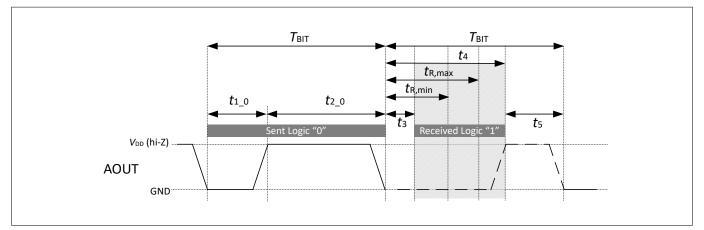

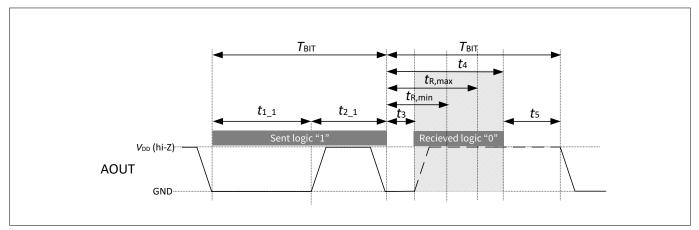

A single bit information sent by the microcontroller is encoded as a PWM waveform for which the duty-cycle is defined as follows:

- Logic "0" is sent as a short low  $(0.3^*T_{BIT})$  and long high  $(0.7^*T_{BIT})$  PWM pulse;

- Logic "1" is sent as a long low  $(0.7^*T_{BIT})$  and short high  $(0.3^*T_{BIT})$  PWM pulse.

The typical threshold level to detect a logic "0" during a high to low transition and for logic "1" during low to high transition are shown in Table 1.

An example of a 1 bit transmission sending a logic "0" to the device by receiving a logic "1" can be seen in the following figure. The initial pulse length is defined by  $t_{1_0}$  and  $t_{2_0}$ . When sending a logic "0" to the device the low time  $t_{1_0}$  has to be shorter than the high time  $t_{2_0}$ . The response time  $t_4$  is depending on the low time  $t_{1_0}$  and high time  $t_{2_0}$  as described in the following table. The grey square marks the time window when reading shall be performed by the microcontroller. Read access shall be performed starting at half of the  $t_4$  time window, as specified by the reading time  $t_R$ . During the reading time  $t_R$ , the master shall not drive the AOUT pin. All parameters are described in the following table.

### **3** Serial Inspection and Configuration Interface (SICI)

#### Figure 15 Logic "0" Duty Cycle Waveform

The following figure shows an example of a 1 bit transmission sending logic "1" to the device by receiving logic "0".

| Figure 16  | Logic "1" Duty Cycle Waveform |

|------------|-------------------------------|

| I IGMIC TO |                               |

#### Table 2SICI interface timings

| Parameter                       | Symbol                | Min. | Тур. | Max. | Unit | Note                                                                                                         |

|---------------------------------|-----------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------|

| Interface<br>pre-enable<br>time | t <sub>PRE_IFEN</sub> | -    | -    | 100  | μs   | The user can start forcing<br>AOUT to GND during this<br>time window.                                        |

| Interface<br>enable time        | t <sub>IFEN</sub>     | 300  | -    | -    | μs   | AOUT must be forced to<br>GND before the end of this<br>time window in order to<br>enter the SICI interface. |

| Period time<br>of 1 bit         | T <sub>BIT</sub>      | 40   | -    | 7500 | μs   | It defines the time to<br>transmit 1 bit between<br>the device and a<br>microcontroller.                     |

### **3** Serial Inspection and Configuration Interface (SICI)

| Parameter               | Symbol                | Min. | Тур.                                              | Max. | Unit                       | Note                                                                                                                                                                                          |

|-------------------------|-----------------------|------|---------------------------------------------------|------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low time<br>sending 0   | t <sub>1_0</sub>      | 28   | 33                                                | 38   | % of T <sub>BIT</sub>      | It defines the first low<br>time of a bit. The low time<br>has to be shorter than the<br>next high time to send a<br>logic 0 bit to the device.<br>Every bit has to start with<br>a low time. |

| Low time<br>sending 1   | t <sub>1_1</sub>      | 62   | 67                                                | 72   | % of T <sub>BIT</sub>      | It defines the first low<br>time of a bit. The low time<br>has to be longer than the<br>next high time to send a<br>logic 1 bit to the device.<br>Every bit has to start with<br>a low time.  |

| High time<br>sending 0  | t <sub>2_0</sub>      | -    | T <sub>BIT</sub> -t <sub>1_0</sub>                | -    | μs                         | It defines the first high<br>time after the low time<br>of a single bit. In order<br>to send a logic 0 to the<br>device the high time has<br>to be longer than the<br>previous low time.      |

| High time<br>sending 1  | t <sub>2_1</sub>      | -    | <i>T</i> <sub>BIT</sub> - <i>t</i> <sub>1_1</sub> | -    | μs                         | It defines the first high<br>time after the low time<br>of a single bit. In order<br>to send a logic 1 to the<br>device the high time has<br>to be shorter than the<br>previous low time.     |

| Low time<br>before read | <i>t</i> <sub>3</sub> | 10   | -                                                 | 30   | % of <i>t</i> <sub>4</sub> | Increase of this time will<br>reduce sensor response<br>time $t_4$ . Therefore $t_R$ has<br>to be set accordingly.                                                                            |

|                         |                       |      |                                                   |      |                            | The AOUT pin has to<br>be forced to GND after<br>the first high time of a<br>transmitted bit to initiate<br>the response sequence.                                                            |

| Reading<br>time         | t <sub>R</sub>        | 50   | -                                                 | 80   | % of <i>t</i> 4            | The device drives AOUT to $V_{\text{DD}}$ by default. Set the external controller in tristate.                                                                                                |

### Table 2 (continued) SICI interface timings

### **3** Serial Inspection and Configuration Interface (SICI)

| Parameter                 | Symbol                | Min.                                          | Тур.                             | Max.                                                                                                                                             | Unit | Note                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|-----------------------|-----------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Response<br>time          | <i>t</i> <sub>4</sub> | 2 * ABS(t <sub>1_x</sub> - t <sub>2_x</sub> ) | -                                | -                                                                                                                                                | μs   | During this time, the<br>AOUT pin is driven from<br>the device. Therefore, the<br>master shall not drive<br>the AOUT pin. The device<br>drives the AOUT either<br>to GND or V <sub>DD</sub> .The<br>master shall sample/read<br>the AOUT pin level for<br>the response within the<br>defined time window<br>specified by parameter t <sub>R</sub> .                               |

| Time<br>between 2<br>bits | <i>t</i> <sub>5</sub> | 1                                             | T <sub>BIT</sub> -t <sub>4</sub> | 5400                                                                                                                                             | μs   | The maximum high time<br>between two bits is<br>limited by the maximum<br>allowed high time. By<br>exceeding the maximum<br>high time, the interface is<br>deactivated and can only<br>be entered after restarting<br>the device.                                                                                                                                                 |

| Max high<br>time          | t <sub>HIGH</sub>     | 1                                             | -                                | 5400 μs Only va<br>bit high<br>no rest<br>betwee<br>If AOUT<br>than th<br>high tir<br>commu<br>and the<br>workin<br>operati<br>a new o<br>sensor |      | <ul> <li>Only valid for a single bit high time. There is no restriction in timing between two commands.</li> <li>If AOUT stays at V<sub>DD</sub> longer than the defined max high time thigh, the SICI communication is closed and the sensor starts working in the defined operating mode. To start a new communication the sensor shall be powered off and on again.</li> </ul> |

| Min low time              | t <sub>LOW</sub>      | 1                                             | -                                | 5400                                                                                                                                             | μs   | If AOUT stays at GND<br>longer than the defined<br>max of minimum low time<br>the SICI communication<br>is closed and the<br>sensor starts working in<br>the defined operating<br>mode. To start a<br>new communication the<br>sensor shall be powered<br>off and on again.                                                                                                       |

### Table 2 (continued) SICI interface timings

#### **3 Serial Inspection and Configuration Interface (SICI)**

| Parameter            | Symbol                    | Min. | Тур. | Max. | Unit | Note                                                           |

|----------------------|---------------------------|------|------|------|------|----------------------------------------------------------------|

| ISM settling<br>time | T <sub>ISM_SETTLING</sub> | -    | -    | 100  | μs   | Time needed after ISM reactivation for AOUT voltage to settle. |

#### Table 2 (continued) SICI interface timings

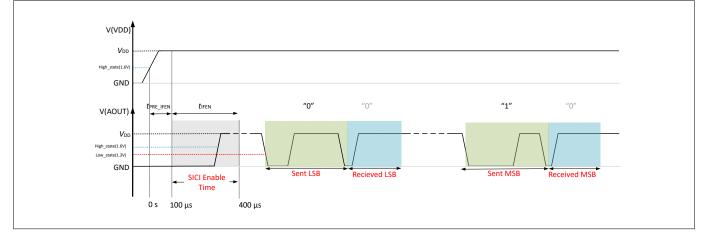

### 3.4 SICI activation

The AOUT pin must be driven using a specific timing to ensure the correct enabling of the SICI communication between the sensor and microcontroller. The external microcontroller must be able to control the sensor supply voltage in order to meet the correct timing and successfully activate the interface. The steps for correctly entering the SICI are the following; in the figure below, the green highlighted squares indicate the received bits, while the blue highlighted squares indicate the bits sent by the sensor:

- The output buffer of the sensor (open drain with internal pull-up) keeps the AOUT pin to V<sub>DD</sub> during the high impedance state of the GPIO pin of the external microcontroller, within the first 400 µs after supplying the device;

- The AOUT pin has to be driven by the external microcontroller to GND for  $t_{LOW}$  time within the defined time window of  $t_{IFEN}$ . The GPIO pin of the external microcontroller must support tri-state configuration to allow the sensor to reply. This low state is only necessary after startup to allow the device to be prepared to receive the 16 bits enter-interface command (password). The activation will also work if the AOUT stays at GND from the beginning onwards. There is no need to set the AOUT to  $V_{DD}$  before forcing it to GND;

- After releasing the AOUT back to V<sub>DD</sub> send the 16 bits enter-interface command with LSB first from the microcontroller. While sending the SICI enter-interface command, the device answers to each sent bit with logic "0";

- After a correct enter-interface command has been sent, the AOUT pin will remain at V<sub>DD</sub> being in open-drain mode. Otherwise, the AOUT pin will reflect the quiescent voltage if the interface activation is unsuccessful.

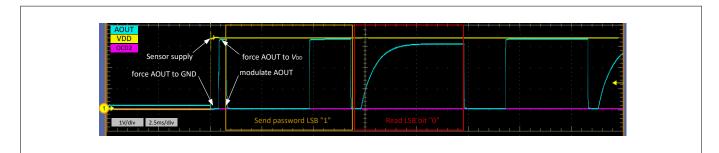

#### Figure 17 Enabling SICI after device startup

The figure below shows the real time oscilloscope figure which describes the interface activation by modulating the AOUT after startup. The modulation of the first two password bits can be seen in the oscilloscope picture. The user must make sure that microcontroller does not drive the AOUT pin to high during the sensor reply, i.e. Read LSB bit "0" in the figure below, to avoid the AOUT pin drawing an excessive amount of current.

#### 3 Serial Inspection and Configuration Interface (SICI)

#### Figure 18 SICI enter interface sequence

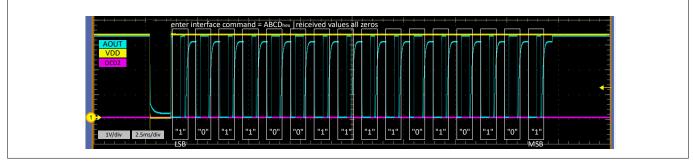

The figure below shows the oscilloscope picture of the complete 16 bits command which is necessary to activate the sensor interface. The PWM modulation of each sent bit followed by the answer bits are visible. After sending the enter-interface command, the next falling edge of the AOUT will start the subsequent 16 bits commands.

Figure 19

SICI enter-interface command

#### **3 Serial Inspection and Configuration Interface (SICI)**

### **3.5 SICI standard commands**

A typical SICI communication consists of multiple input commands transmitted over AOUT via the same voltage modulation as used for the enter-interface command, followed by a command including the access information and address. The sensor replies with the data of a previous command. The sent data stream is initiated by the microcontroller starting with the LSB first and the receiving sequence is driven by the device. The reply data stream sent by the device starts with the LSB first.

The following three tables describe the microcontroller command frame bit and the standard interface commands.

| 15  | 14  | 13 | 12 | 11 | 10   | 9         | 8 | 7 | 6 | 5 | 4     | 3   | 2 | 1 | 0 |

|-----|-----|----|----|----|------|-----------|---|---|---|---|-------|-----|---|---|---|

| w/r | PR# | 0  |    |    | ADDR | ADDR[6:0] |   |   |   | 1 | LEN[3 | :0] | 1 |   |   |

### Table 3Microcontroller Command Frame

| Table 4 | Microcontroller Command Bit Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|---------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bits    | Name                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 3:0     | LEN                                     | These 4 bits define the burst length i.e. the number of data frames following the command frame for read and write accesses as LEN + 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|         |                                         | The burst length is important especially for write accesses, as all<br>frames from the master are treated as data frames. The address<br>is incremented automatically by the interface starting with the<br>initial address in the command frame until the burst length has<br>been reached.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 10:4    | ADDR                                    | Initial 7 bits address used for read and write accesses. Note<br>that the address will simply wrap around internally, if the access<br>reaches the end of the address space (128 words), but the burst<br>length is not reached yet.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 13:11   | -                                       | These bits need to be set to "0", as they are used to identify NOP commands. Therefore, a NOP command with usually all bits set to "1" is ignored by the interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 14 PR#  |                                         | "0" means, the interface performs a read-out of the initially<br>addressed register and sends back the current data while<br>receiving the first write data frame. On successive write data<br>frames, the new content of the previously written register<br>address is send back to the master. To get all the new register<br>content e.g. an additional NOP frame would have to be sent at<br>last, as it is done for a read access. Note that these pre and pos<br>reads during a write access will also affect clear-on-read bits (e<br>status bits). Therefore, it is suggested to set this bit to "1", if in<br>doubt. |  |  |  |  |  |

|         |                                         | "1" means, pure write access to addressed registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

### **3** Serial Inspection and Configuration Interface (SICI)

#### Table 4 (continued) Microcontroller Command Bit Description

| Bits | Name | Description                                                                                                                                                                                                                                                                                              |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | w/r  | "0" means read access. To receive the data requested for readout<br>NOP frames (frame content set to all ones) have to be send for<br>the given burst length. A frame that does not have at least bits<br>13:11 set to "1" will be interpreted as a new command and thus<br>can interrupt a read access. |

|      |      | "1" means write access. All the following frames within the burst<br>length will be treated as write data frames. Therefore, a write<br>access cannot be interrupted.                                                                                                                                    |

| Table 5 | Commonly Used Commands |

|---------|------------------------|

|---------|------------------------|

| Command name                           | Address                                | Command / Data             | Description                                                                                                                                                     |  |  |

|----------------------------------------|----------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Enter-interface command                | -                                      | ABCD <sub>hex</sub>        | Activate communication.                                                                                                                                         |  |  |

| Power down ISM                         | 25 <sub>hex</sub>                      | 8000 <sub>hex</sub>        | Reserve if-access to the<br>EEPROM data bus to avoid<br>that ISM is blocking the<br>data bus.                                                                   |  |  |

| Disable failure indication             | 01 <sub>hex</sub>                      | 0000 <sub>hex</sub>        | Disabling internal safety<br>mechanism reactions<br>(except overvoltage).                                                                                       |  |  |

| Write command                          | 40 <sub>hex</sub> to 42 <sub>hex</sub> | 8402 <sub>hex</sub> / XYXY | Initialize write command<br>to address 40 <sub>hex</sub> . Send<br>data XYXY to previous<br>addressed line where<br>XYXY stand for 16 bits data<br>placeholder. |  |  |

| Read command                           | 40 <sub>hex</sub> to 51 <sub>hex</sub> | 0400 <sub>hex</sub>        | Initialize read command<br>at address 40 <sub>hex</sub> .                                                                                                       |  |  |

| Read command                           | 41 <sub>hex</sub>                      | 0410 <sub>hex</sub>        | Initialize read command<br>at address 41 <sub>hex</sub> . Read<br>data from previous<br>address 40 <sub>hex</sub> .                                             |  |  |

| Read command                           | 51 <sub>hex</sub>                      | 0510 <sub>hex</sub>        | Initialize read command<br>at address 51 <sub>hex</sub> . Read<br>data from previous<br>address.                                                                |  |  |

| NOP                                    | -                                      | FFFF <sub>hex</sub>        | No operation command,<br>to read former addressed<br>values.                                                                                                    |  |  |

| EEPROM set all zeros 3E <sub>hex</sub> |                                        | 0248 <sub>hex</sub>        | Set all EEPROM bits to zero.                                                                                                                                    |  |  |

| EEPROM set all ones                    | 3E <sub>hex</sub>                      | 024B <sub>hex</sub>        | Set all EEPROM bits to one.                                                                                                                                     |  |  |

| EEPROM refresh                         | 3E <sub>hex</sub>                      | 024C <sub>hex</sub>        | Refresh all EEPROM lines.                                                                                                                                       |  |  |

(table continues...)

User manual

#### **3 Serial Inspection and Configuration Interface (SICI)**

#### Table 5(continued) Commonly Used Commands

| Command name         | Address           | Command / Data                            | Description                        |

|----------------------|-------------------|-------------------------------------------|------------------------------------|

| EEPROM program zeros | 3E <sub>hex</sub> | 024E <sub>hex</sub>                       | Program all set zeros into EEPROM. |

| EEPROM program ones  | 3E <sub>hex</sub> | C3E0 <sub>hex</sub> / 024F <sub>hex</sub> | Program all set ones into EEPROM.  |

To each command the sensor replies with the previous addressed data except while sending the enter-interface command; in that case, the device replies with all zeros. That means, there is always a delay of one command between the requested command and the respective data. For example, if a new read command is sent to the sensor, then it replies with the data of the previous command.

Therefore a read sequence consists of the read command with the requested address followed by a second command to receive the previous addressed data. The second command can either be a read or write command to address the next line.

|                  | read one address                                        |                                                               |                       |

|------------------|---------------------------------------------------------|---------------------------------------------------------------|-----------------------|

| Master to Sensor | "0" "0" "0" address "0000"                              | 16 bit "NOP" command                                          |                       |

| Sensor to Master | 16 bit don't care                                       | 16 bit addressed data                                         |                       |

|                  | read                                                    |                                                               |                       |

| Master to Sensor | "0"     2 bit<br>access     8 bit<br>address     "0000" | "0"         2 bit access         8 bit address         "0000" | 16 bit "NOP" command  |

| Sensor to Master | 16 bit don't care                                       | 16 bit addressed data                                         | 16 bit addressed data |

#### Figure 20 SICI Read Sequence

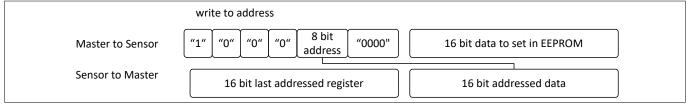

To perform a write command to a register, the MSB of the command has to be set to "1". A write sequence consists of two SICI frames of 16 bits. After each write command, the device is expecting further 16 bits of data.

#### Figure 21 SICI Write Sequence

### 3.6 Internal temperature readout example

The temperature value can be read via the SICI interface. The following example describes the required command sequence to enter the interface and read out the 16 bits temperature value. In the following table, the commands with the correct timing order and the required minimum time are listed. The temperature measurement sensitivity is 16 LSB/°C. The ADC value corresponding to 25 °C is 1408<sub>dec</sub>. The following formula describes how to calculate the temperature depending on the 16 bits value.

$$Temperature \left[ {}^{\circ}C \right] = \frac{ADC_{VALUE} - 2048}{16} + 65$$

(5)

#### 3 Serial Inspection and Configuration Interface (SICI)

| Table 6                                       | Command sec           | quence example to read out the internal 16 bits temperature value        |

|-----------------------------------------------|-----------------------|--------------------------------------------------------------------------|

| Command / Data                                | Minimum<br>frame time | Description                                                              |

| ABCD <sub>hex</sub>                           | 0.64 ms               | Enter-interface command (send user password).                            |

| Write command to<br>address 25 <sub>hex</sub> | 0.64 ms               | Power down ISM (write command).                                          |

| 8000 <sub>hex</sub>                           | 0.64 ms               | Power down ISM (data).                                                   |

| Read command at<br>address 18 <sub>hex</sub>  | 0.64 ms               | Sending the address to read the temperature value.                       |

| FFFF <sub>hex</sub>                           | 0.64 ms               | Reading the data by sending the next command or sending the NOP command. |

Power cycle the device to activate normal operating mode. Alternatively set the device in normal operating mode by sending the following commands.

| Write command to<br>address 25 <sub>hex</sub> | 0.64 ms | Power on ISM (write command). |

|-----------------------------------------------|---------|-------------------------------|

| 0000 <sub>hex</sub>                           | 0.64 ms | Power on ISM (data).          |

Wait until the AOUT settles back into calibrated mode. This can take up to *T*<sub>ISM\_SETTLING</sub>. In calibrated mode, the AOUT reflects the voltage level of the VREF pin, assuming that no current flows through the primary current rail of the device.

#### **4 Internal registers and EEPROM content**

# 4 Internal registers and EEPROM content

### 4.1 Internal registers

Apart from the EEPROM content, the user needs to fetch and write data into the following registers during the calibration procedure. The register address lines that correspond to Gain Code Word, Offset Code Word and internal temperature are shown in the following tables. Each address line consists of 16 bits.

#### Table 7Internal temperature register. Address 18

|                  |    |    |    | -  |    | - |   |   |   |   |   |   |   |   |   |

|------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 15               | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| T <sub>INT</sub> |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Before accessing the register above, the user needs to disable the ISM.

#### Table 8Gain Code Word register. Address 20

| 15 | 14 | 13 | 12 | 11 | 10    | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|-------|----|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    | Gain_ | CW |   |   |   |   |   |   |   |   |   |

Before accessing the register above, the user needs to disable the ISM.

#### Table 9 Offset Code Word register. Address 21<sub>hex</sub>

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|--------|----|---|---|---|---|---|---|

|    |    |    |    |    |    |   |   | Offset | CW |   |   |   |   |   |   |

Before accessing the register above, the user needs to disable the ISM. This register is in sign-magnitude representation.

#### Table 10SICI bypass register. Address 25

| 15          | 14 | 13 | 12            | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|----|----|---------------|----|----|---|---|---|---|---|---|---|---|---|---|

| test_pd_ism |    |    | SICI_mode_dis |    |    |   |   |   |   |   |   |   |   |   |   |

Set the 15<sup>th</sup> bit to "1" to power down the ISM for undisturbed access to all registers through interface. Note that ISM will be deactivated almost immediately, but reactivation and return to normal firmware execution can take up to  $T_{\text{ISM}\_\text{SETTLING}}$ . Please refer to the timing specifications in Table 2.Set the 12<sup>th</sup> bit to "1" to put the AOUT buffer in normal operating mode, if the device is in SICI interface mode. Note that the SICI interface is not available anymore after setting this bit. To restart the SICI, enter the SICI enter-interface command after chip reset.

#### Table 11Diagnosis mode amplitude register. Address 16

| 15            | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Diag_mode_amp |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Set the 15<sup>th</sup> bit to "0" to reduce the amplitude of analog signal and OCD thresholds during the diagnosis mode execution with respect to default values.

*Note:* For writing into internal registers, the user has to enter the SICI interface by using the trimming password "DCBA<sub>hex</sub>".

#### **4 Internal registers and EEPROM content**

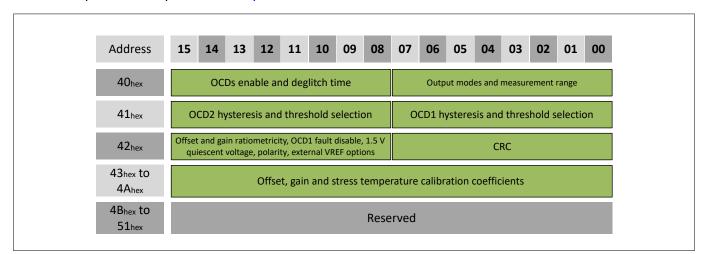

### 4.2 EEPROM content

This chapter gives an overview of the programmable content of the current sensor. The sensor's nonvolatile memory (EEPROM) is organized in 16 bits registers which can be addressed individually. The storage space is separated into two areas, user area with read/write access and the read only area (can actually be written, but it is not programmable). Address lines indicated in green are accessible for the user and can be set according to individual application requirements. Addresses from  $4B_{hex}$  to  $51_{hex}$  are usually not to be changed by the user.

When the EEPROM content is reprogrammed a CRC check register has to be updated. The user has to calculate the new CRC value by reading the entire EEPROM content, which corresponds to 18 lines. An incorrect CRC value leads to an error detection by an internal safety mechanism of the device. In case of a CRC error, the OCD open drain outputs are set to GND. A detailed description of the user accessible content and the CRC calculation procedure explained in Chapter 5.1.

#### Figure 22 EEPROM Overview

#### Table 12Functional description of address line 40

| Bit field name           | Bit   | Туре | Bit field description                                                                                                                                                |

|--------------------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEAS <sub>RNG</sub>      | 4:0   | rw   | The measurement range bits define the mV/mT sensitivity according to the values reported in the product datasheet [1]. Further information are listed in Table 21.   |

|                          |       |      | The standard setting is S3.                                                                                                                                          |

| OP <sub>MODE</sub>       | 6:5   | rw   | The output mode can be set according to Table 21.                                                                                                                    |

|                          |       |      | The standard setting is the semi-differential mode.                                                                                                                  |

| OCD1 <sub>DEGLITCH</sub> | 9:7   | rw   | The deglitching time of the OCD1 can be set according to Table 21.                                                                                                   |

|                          |       |      | The standard setting is 0 (no additional delay).                                                                                                                     |

| OCD2 <sub>DEGLITCH</sub> | 13:10 | rw   | The deglitching time of the OCD2 can be set according to Table 21.                                                                                                   |

|                          |       |      | The standard setting is 0 (no additional delay).                                                                                                                     |

| OCD1 <sub>EN</sub>       | 14    | rw   | This setting does not influence the error indication for an internal fault response or of the firmware based safety mechanisms, but only the over-current detection. |

|                          |       |      | The standard setting is 1, that means enabled.                                                                                                                       |

### 4 Internal registers and EEPROM content

| Table 12           | (continued) Functional description of address line 40 <sub>hex</sub> |    |                                                                                                                                                                                                                              |  |

|--------------------|----------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OCD2 <sub>EN</sub> | 15                                                                   | rw | This setting does not influence the error indication for an<br>internal fault response or of the firmware based safety<br>mechanisms, but only the over-current detection.<br>The standard setting is 1, that means enabled. |  |

| Table 13              | Function | Functional description of address line 41 <sub>hex</sub> |                                                                                                                                                                                                     |  |  |

|-----------------------|----------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit field name        | Bit Type |                                                          | Bit field description                                                                                                                                                                               |  |  |

| OCD1 <sub>HYST</sub>  | 1:0      | rw                                                       | The hysteresis level of the over-current detection channel 1<br>shall be set according to the full scale in Table 21.<br>The standard setting is 3 <sub>hex</sub> .                                 |  |  |

| OCD1 <sub>THRSH</sub> | 7:2      | rw                                                       | 6 bits value. Over-current detection threshold calculation formulas are reported in product datasheet [1]. The standard setting is C <sub>hex</sub> .                                               |  |  |

| OCD2 <sub>HYST</sub>  | 9:8      | rw                                                       | The hysteresis level of the OCD2 shall be set according to the full scale in Table 21.<br>The standard setting is 3 <sub>hex</sub> .                                                                |  |  |

| OCD2 <sub>THRSH</sub> | 15:10    | rw                                                       | 6 bits value. Over-current detection threshold calculation formulas are reported in product datasheet [1].<br>The standard setting is F <sub>hex</sub> for VSON variant, 10 <sub>hex</sub> for TDSO |  |  |

|                       |          |                                                          | variant.                                                                                                                                                                                            |  |  |

Table 14

Functional description of address line 42<sub>hex</sub>

| Bit field name          | Bit  | Туре | Bit field description                                                                                                                                                                                             |  |

|-------------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CRC                     | 7:0  | rw   | CRC checksum over whole EEPROM content.                                                                                                                                                                           |  |

| VREF <sub>EXT</sub>     | 10:8 | rw   | The external V <sub>REF</sub> bits have to be set according to the external applied reference voltage on the V <sub>REF</sub> pin.<br>The standard setting is 1.65 V. This only applies in single-<br>ended mode. |  |

| Polarity <sub>INV</sub> | 11   | rw   | Output polarity inversion: 0 = disable (default polarity), 1 = enable (inverted polarity).<br>The standard setting is 0.                                                                                          |  |

| QV <sub>1V5SD</sub>     | 12   | rw   | Semi-differential bidirectional and fully differential mode<br>only. 1.5 V quiescent voltage enable: 0 = disabled, 1 = enable.<br>The standard setting is 0.                                                      |  |

| OCD1 <sub>FONLY</sub>   | 13   | rw   | OCD1 fault signal disable: 0 = fault signal on both OCDs, 1 = no<br>fault signal on OCD1.<br>The standard setting is 0.                                                                                           |  |

| RATIO <sub>GAIN</sub>   | 14   | rw   | Gain ratiometricity option: 0 = disable, 1 = enable.<br>The standard setting is 0.                                                                                                                                |  |

#### 4 Internal registers and EEPROM content

| Table 14             | (continu | ed) Functiona | al description of address line 42 <sub>hex</sub>                                                                         |  |  |

|----------------------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| RATIO <sub>OFF</sub> | 15       | rw            | The ratiometric offset behavior of the quiescent voltage is activated if the bit is set to one. 0 = disable, 1 = enable. |  |  |

|                      |          |               | The standard setting is 0.                                                                                               |  |  |

| Table 15             | Function | al descriptio | n of address line 43 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

| g_base_3_0           | 3:0      | rw            | Base gain compensation factor: 4 lowest significant bits of the 11 bits value.                                           |  |  |

| g_tc_tl              | 15:4     | rw            | Gain temperature coefficient linear (signed).                                                                            |  |  |

| Table 16             | Function | al descriptio | n of address line 44 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

| g_base_9_4           | 5:0      | rw            | Base gain compensation factor: 6 intermediate/middle significant bits of the 11 bits value.                              |  |  |

| g_tc_tq              | 15:6     | rw            | Gain temperature coefficient quadratic (signed).                                                                         |  |  |

| Table 17             | Function | al descriptio | n of address line 45 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

| s_base_3_0           | 3:0      | rw            | Stress base value: 4 lower significant bits of the 12 bits value.                                                        |  |  |

| g_base_10            | 4        | rw            | Base gain compensation factor: single most significant bit of the 11 bits value.                                         |  |  |

| g_tc_tt              | 15:5     | rw            | Gain temperature coefficient cubic (signed).                                                                             |  |  |

| Table 18             | Function | al descriptio | n of address line 48 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

| o_base               | 7:0      | rw            | Base offset compensation factor (signed).                                                                                |  |  |

| epk_base             | 15:8     | rw            | EPK stress base value (signed).                                                                                          |  |  |

| Table 19             | Function | al descriptio | n of address line 49 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

| o_tc_tl              | 7:0      | rw            | Offset temperature coefficient linear (signed).                                                                          |  |  |

| epk_tc_tl            | 15:8     | rw            | EPK stress temperature coefficient linear (signed).                                                                      |  |  |

| Table 20             | Function | al descriptio | n of address line 50 <sub>hex</sub>                                                                                      |  |  |

| Bit field name       | Bit      | Туре          | Bit field description                                                                                                    |  |  |

|                      | 1        |               |                                                                                                                          |  |  |

### 4 Internal registers and EEPROM content

| Bit field parameter name | Description                                                                                                |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| MEAS <sub>RNG</sub>      | • 05 <sub>hex</sub> = S1;                                                                                  |  |  |

|                          | • 06 <sub>hex</sub> = S2;                                                                                  |  |  |

|                          | • 08 <sub>hex</sub> = \$3;                                                                                 |  |  |

|                          | • 0C <sub>hex</sub> = S4;                                                                                  |  |  |

|                          | • 10 <sub>hex</sub> = S5;                                                                                  |  |  |

|                          | • 18 <sub>hex</sub> = \$6.                                                                                 |  |  |

| OP <sub>MODE</sub>       | • 0 <sub>hex</sub> = SD <sub>BID</sub> (Semi-differential bidirectional);                                  |  |  |

|                          | • 1 <sub>hex</sub> = FD (Fully-differential);                                                              |  |  |

|                          | • 2 <sub>hex</sub> = SD <sub>UNI</sub> (Semi-differential unidirectional);                                 |  |  |

|                          | • 3 <sub>hex</sub> = SE (Single-ended).                                                                    |  |  |

| OCD1 <sub>DEGLITCH</sub> | • 0 <sub>hex</sub> = 0 ns;                                                                                 |  |  |

|                          | • $1_{hex} = 500 \text{ ns};$                                                                              |  |  |

|                          | • $2_{hex} = 1000 \text{ ns};$                                                                             |  |  |

|                          | • $3_{hex} = 1500 \text{ ns};$                                                                             |  |  |

|                          | • $4_{hex} = 2000 \text{ ns};$                                                                             |  |  |

|                          | • $5_{hex} = 2500 \text{ ns};$                                                                             |  |  |

|                          | • 6 <sub>hex</sub> = 3000 ns;                                                                              |  |  |

|                          | • 7 <sub>hex</sub> = 3500 ns.                                                                              |  |  |

| OCD2 <sub>DEGLITCH</sub> | • 0 <sub>hex</sub> = 0 ns;                                                                                 |  |  |

|                          | • $1_{hex} = 500 \text{ ns};$                                                                              |  |  |

|                          | • $2_{hex} = 1000 \text{ ns};$                                                                             |  |  |

|                          | • $3_{hex} = 1500 \text{ ns};$                                                                             |  |  |

|                          | • $4_{hex} = 2000 \text{ ns};$                                                                             |  |  |

|                          | • $5_{hex} = 2500 \text{ ns};$                                                                             |  |  |

|                          | • 6 <sub>hex</sub> = 3000 ns;                                                                              |  |  |

|                          | • 7 <sub>hex</sub> = 3500 ns;                                                                              |  |  |

|                          | • $8_{hex} = 4000 \text{ ns};$                                                                             |  |  |

|                          | • $9_{hex} = 4500 \text{ ns};$                                                                             |  |  |

|                          | • A <sub>hex</sub> = 5000 ns;                                                                              |  |  |

|                          | • B <sub>hex</sub> = 5500 ns;                                                                              |  |  |

|                          | • C <sub>hex</sub> = 6000 ns;                                                                              |  |  |

|                          | • D <sub>hex</sub> = 6500 ns;                                                                              |  |  |

|                          | • E <sub>hex</sub> = 7000 ns;                                                                              |  |  |

|                          | • F <sub>hex</sub> = 7500 ns.                                                                              |  |  |

| OCD1 <sub>THRSH</sub>    | 6 bits value. Over-current detection threshold calculation formulas are reported in product datasheet [1]. |  |  |

| OCD2 <sub>THRSH</sub>    | 6 bits value. Over-current detection threshold calculation formulas are reported in product datasheet [1]. |  |  |

| (table continues)        | 1                                                                                                          |  |  |

#### 4 Internal registers and EEPROM content

| Bit field parameter name | Description                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF <sub>EXT</sub>      | <ul> <li>0<sub>hex</sub> = 1.65 V;</li> <li>2<sub>hex</sub> = 1.5 V;</li> <li>3<sub>hex</sub> = 1.8 V.</li> </ul>                                                  |

| OCDX <sub>HYST</sub>     | <ul> <li>0<sub>hex</sub> = 0 * FS;</li> <li>1<sub>hex</sub> = 0.0625 * FS;</li> <li>2<sub>hex</sub> = 0.125 * FS;</li> <li>3<sub>hex</sub> = 0.25 * FS.</li> </ul> |

#### Table 21 (continued) EEPROM parameters description

5 EEPROM programming

# 5 EEPROM programming

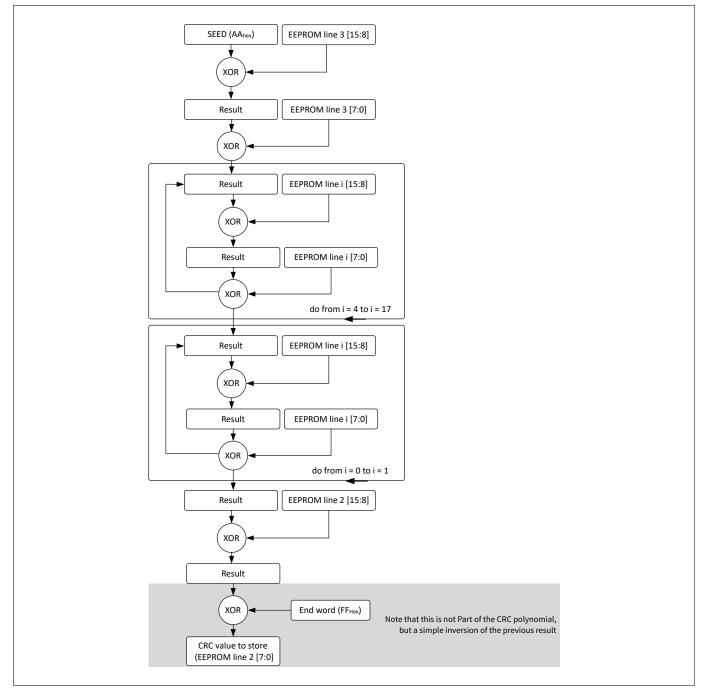

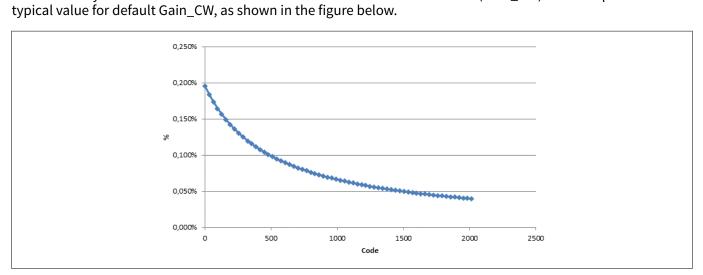

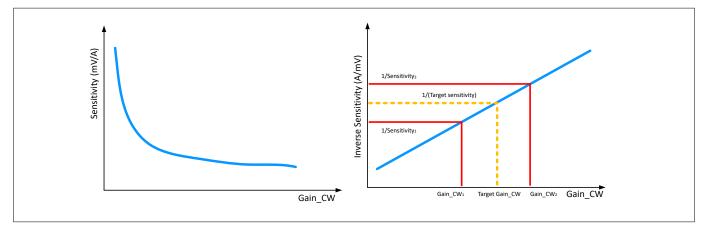

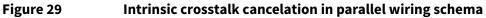

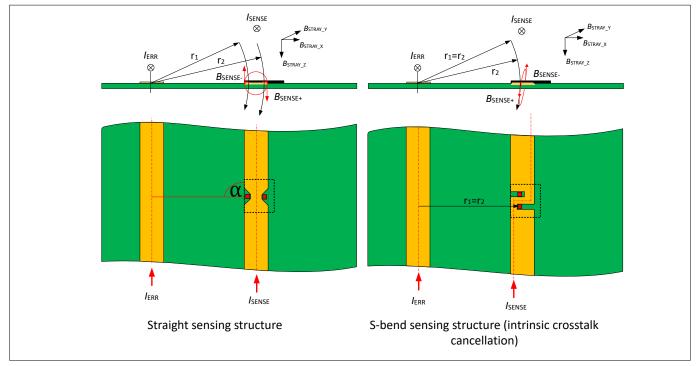

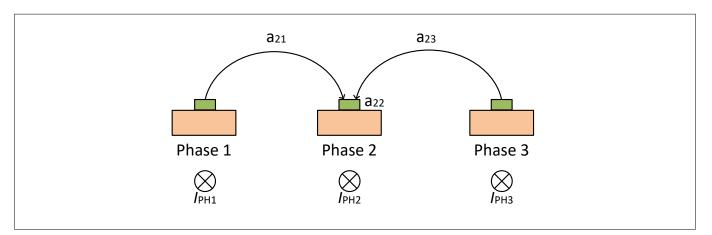

### 5.1 EEPROM CRC calculation