Copyright ©2021 , ATP Electronics Taiwan Inc. All rights reserved

# Chapter 1 **DRAM** Basics

### 1. Dynamic Random-Access Memory (DRAM) Overview 1.1 What is Dynamic Random-Access Memory? 1.2 Main Types of RAM 1.3 How DRAM Stores Data 1.4 Volatile vs. Non-Volatile Memory 1.5 Basic Function of DRAM 2. DRAM IC Architecture 3. Package Types 12 3.1 TSOP 3.2 BGA 3.3 Stacking Technologies to Increase Density 15

| 3. | Generations                     |

|----|---------------------------------|

|    | 3.1 Legacy SDRAM                |

|    | 3.2 DDR1, DDR2, DDR3, DDR4      |

|    | 3.3. DDR5                       |

| 4. | Categories                      |

|    | 4.1 By Form Factor              |

|    | 4.2 By Function                 |

| 5. | Module Organization and Capacit |

| 6. | Applications                    |

30

31

32

36

16 17 19

25

Dynamic Random-Access Memory (DRAM) Overview

### What is Dynamic Random-Access Memory?

DRAM is the hardware in a computer that temporarily stores the operating system (OS), application programs, and working data currently in use.

- It is also known as "main" or "short-term" memory.

- "Random" means data can be accessed (read and changed) directly and in any order.

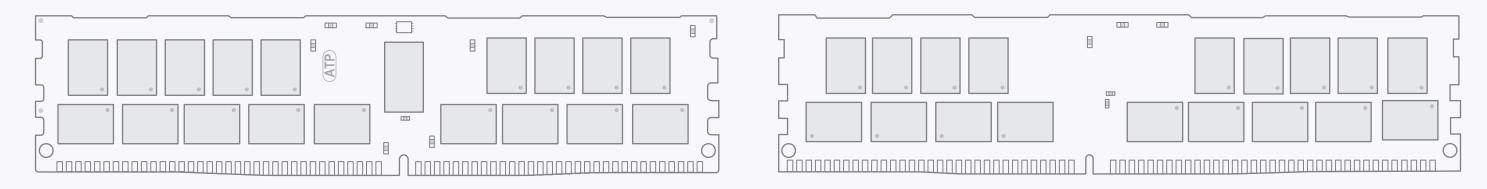

DRAM is installed on the motherboard's memory slots as dual inline memory modules (DIMMs). DIMMs are called as such because they have two independent rows of pins in front and at the back.

Front

### Main Types of RAM

There are two main types of RAM: Dynamic RAM (DRAM) and Static RAM (SRAM).

- DRAM (pronounced DEE-RAM), is widely used as a computer's main memory. Each DRAM memory cell is made up of a transistor and a capacitor within an integrated circuit, and a data bit is stored in the capacitor. Since transistors always leak a small amount, the capacitors will slowly discharge, causing information stored in it to drain; hence, DRAM has to be refreshed (given a new electronic charge) every few milliseconds to retain data.

- SRAM (pronounced ES-RAM), is made up of four to six transistors. It keeps data in the memory as long as power is supplied to the system unlike DRAM, which has to be refreshed periodically. As such, SRAM is faster but also more expensive, making DRAM the more prevalent memory in computer systems.

### How DRAM Stores Data

There are two main types of RAM: Dynamic RAM (DRAM) and Static RAM (SRAM).

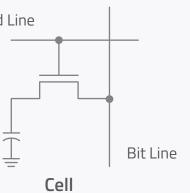

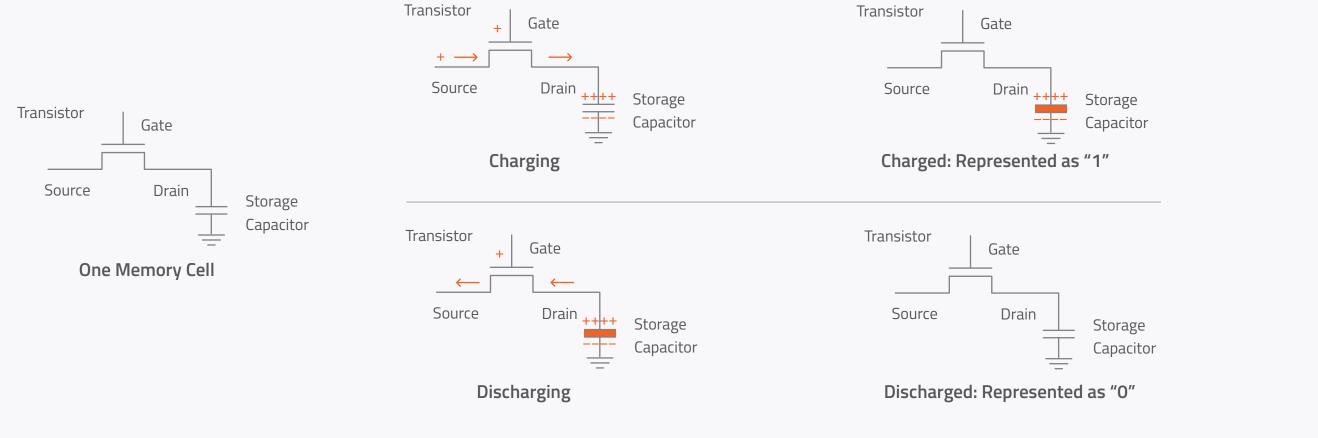

A **memory chip** is made up of transistors and capacitors, which are paired to form a memory cell.

DRAM stores each bit of data in a capacitor within an integrated circuit (IC). The capacitor can either be charged or discharged, representing the two values of a bit: 0 and 1.

The transistor acts a switch, allowing the memory chip controller to read the capacitor or change its state.

#### Bit

The term "bit" is short for binary digit. As the name suggests a bit represents a single digit in a binary number. A bit is the smallest unit of information used in computing system and can have a value of either "1" or "0".

Word Line

-

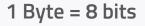

#### Byte

A byte consists of 8 bits. Almost all specifications of computer's capabilities are represented in bytes.

Word Line

Word Line

# Volatile vs. Non-Volatile Memory

| VOLATILE                                  | NON-VOLATILE                                                  |

|-------------------------------------------|---------------------------------------------------------------|

| Internal/Main/Primary memory              | External/Secondary memory                                     |

| Loses data quickly when power is removed  | Data remains stored even if power is removed                  |

| Temporary/short-term storage              | Permanent/long-term storage                                   |

| Faster                                    | Slower                                                        |

| Less storage capacity                     | Generally, has more storage capacity                          |

| Impacts system performance                | Impacts storage capacity                                      |

| CPU can directly access data              | CPU cannot directly access data                               |

| Installed on the motherboard memory slots | May be removable, or embedded/<br>soldered on the motherboard |

### Basic Function of DRAM

Data or program is first stored on non-volatile media, such as a solid state drive (SSD).

The data or program is loaded into the DRAM.

The processor can then access the data or run the program.

If DRAM capacity is too low, it may not be able to hold all the data or programs that the CPU needs, so the RAM keeps going back to the SSD, thus slowing down performance.

# DRAM IC Architecture

|      |        |       |      |       |        |          | 14 i i |     |         |

|------|--------|-------|------|-------|--------|----------|--------|-----|---------|

|      |        |       |      |       | 1      |          |        |     |         |

|      | _      |       |      |       |        |          |        | :   | 1.11    |

|      | 12.00  |       |      |       |        |          |        |     | 1.1     |

|      |        |       |      |       |        |          | 1. I.  |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        | 11       | 1.1.   |     | 1.1.1   |

|      |        |       |      |       |        |          | 4.14   | 1   |         |

|      |        |       |      |       |        |          | 11.00  |     |         |

|      |        |       |      |       |        | 1.1      |        |     |         |

|      |        |       |      |       |        |          | 1.1.1  |     | 1111    |

|      |        |       |      |       |        |          |        | ÷., |         |

|      |        |       |      |       | 1.1    |          |        | •   | 1111    |

|      |        |       |      |       | 1      |          |        | 1   |         |

|      |        |       |      |       | 1      | 1111     | 1.1    | 1   | 11111   |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          |        |     | 1111    |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       | 1111 |       | 1      |          |        | 4   | 1.11    |

|      |        |       | ÷    |       |        |          |        | 1   |         |

|      |        | 1     |      |       |        |          |        |     | 11.1    |

|      |        | 1     | 1.11 |       |        |          |        | 1   | 1.00    |

|      |        |       | 1111 | 1 1 1 |        |          |        |     | that is |

|      |        |       | · ·  |       | •      |          |        | 1   |         |

|      |        |       | 111  |       |        |          | 1.11   |     |         |

|      |        |       |      |       |        | . · ·    | .:     |     |         |

|      |        |       |      |       | 1 1    |          |        |     | 1.1.1   |

|      |        |       |      |       |        |          |        |     | 16      |

|      |        |       |      |       |        |          | . 1    |     |         |

|      |        |       |      |       |        |          |        |     | 1.1     |

|      |        |       |      |       |        |          | 125    |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          |        |     | 1.1.1   |

|      |        |       |      |       |        | 28 H N   |        |     | 1111 L  |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        | - 1 I    |        |     |         |

|      |        |       |      |       |        |          |        |     | 1.11    |

|      |        |       |      |       |        |          |        | 1   |         |

|      |        |       |      |       |        | 18 e e . |        |     | 1111    |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        | 1        | ÷      |     |         |

|      |        |       |      |       |        |          |        | •   |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       | 1 de 1 |          | 1.11   |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          | A      |     |         |

|      |        |       |      |       |        |          | 8 C 8  |     |         |

| 111  |        |       |      | 1.1   |        | **       |        |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          | _      |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          |        |     |         |

| 1.1  |        |       |      |       |        |          |        |     |         |

| 12.0 | -      |       |      |       |        | 1.       |        |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      |       |        |          |        |     |         |

|      |        |       |      | Sec   |        |          |        |     |         |

|      |        |       |      |       |        |          |        |     |         |

| 1.1  |        |       |      |       |        |          |        |     |         |

| 1    |        |       |      |       |        |          |        |     |         |

| 1    | 100    | 100 C |      |       |        |          |        |     |         |

|      | Sec. 1 |       |      |       |        |          | 2 2 1  |     |         |

## Memory Cell

Charge & Discharge

- DRAM stores each bit of data in a separate capacitor within an integrated circuit.

- The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1.

- Volatile memory: requires power to maintain the stored information.

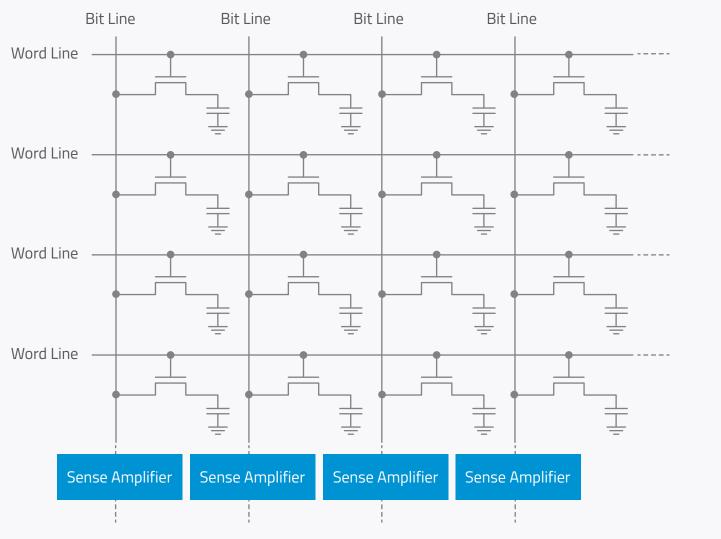

### Memory Cell Array

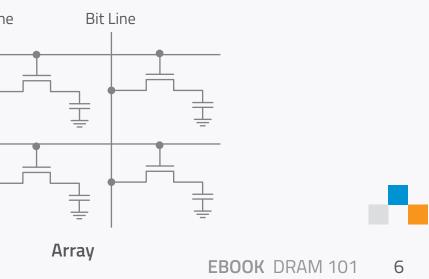

• The memory cells are arranged in a two-dimensional array connected by word line and bit lines.

- Differential Sense Amplifiers are connected to each bit line.

- Compare the new bit line voltages with the original voltages.

- Temporarily store the voltages values read from the cell in the flip-flop latch circuitry.

- Output one of the values to data bus.

# Package Types

## Package Types

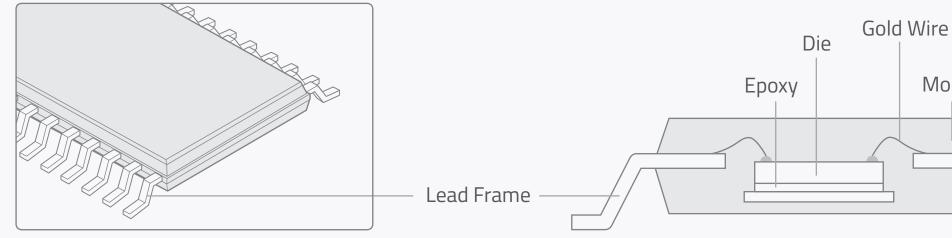

### TSOP (Thin Small Outline Package)

TSOP is a type of surface mount packaging for integrated circuits (IC). It has a very thin and low profile and tight lead spacing. It is rectangular in shape and comes in two configurations: TSOP1 has the leads on the ends or short edges of the package while TSOP2 has the leads on the sides or long edges of the package. The pins have an "L" shape ("gull-wing leads" according to JEDEC) and the package is typically made of plastic and ceramic.

TSOP is used on ATP SDRAM/DDR modules.

Molding

# Package Types

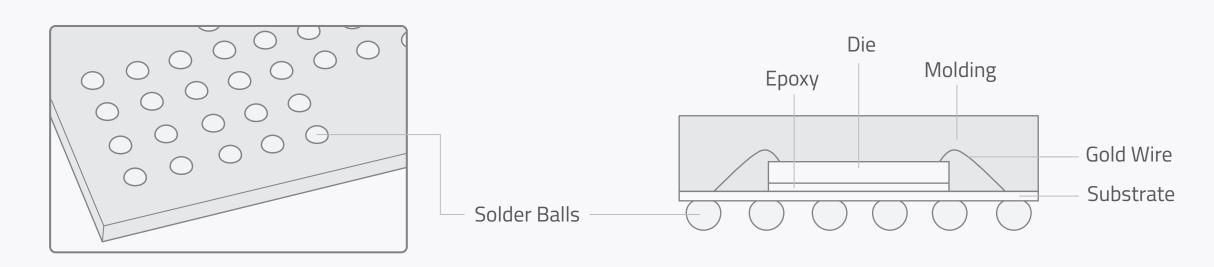

### BGA (Ball Grid Array)

BGA is a type of surface mount packaging for integrated circuits (IC). It uses a grid of solder balls attached to the substrate. The entire bottom surface is used and not just the perimeter, hence providing more interconnection pins. The leads to the balls are also shorter, enabling better performance at faster speeds. • The transition from TSOP to BGA happened around DDR1 to fit into the small outline PCB by maximum density per IC quantity, especially

- for high-density SO-DIMM.

- Main benefit: The thermal specification Ta (ambient) of the DRAM module increased from 70°C to 85°C, since the BGA design allows better heat conduction between the IC package and PCB, preventing the chip from overheating.

BGA package is used on ATP DDR1/2/3/4/5, SDP\*, DDP\* and TSV\*.

\* SDP: Single-Die Package DDP: Dual-Die Package TSV: Through-Silicon Vias

### Stacking Technologies to Increase Density

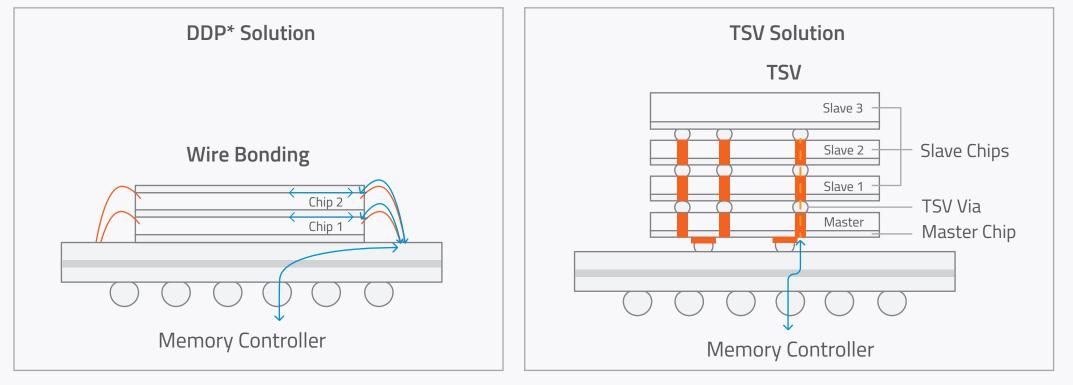

A DRAM IC may have multiple stacks of memory dies to increase density. Stacking is used only for module configurations that absolutely need the increased densities that single-die packaging (SDP) cannot support. The following illustrations show conventional DDP\* solution with wire bonding methods and Through Silicon Via (TSV) technology solution.

BGA DDP\* Solution: DDR3/DDR4/DDR5 modules

\* DDP: Dual-Die Package

Through-Silicon Vias 3-Dimensional Stacking (TSV 3DS) Solution — 3DS, 4H, 8H\*\*: DDR4/DDR5 modules

\*\* 4H, 8H: Refers to die stacking height

Only the Master chip communicates with the Memory Controller regardless of the stacking.

#### **TSV Advantages:**

- Higher density

- Better data transfer rate

- Reduces interconnect delay

- Better signal integrity and performance

- Lower power consumption

# Generations

## Legacy SDRAM: SDR vs. DDR

Synchronous Dynamic Random-Access Memory (SDRAM) refers to memory that operates synchronously with the system clock. The synchronous interface enables the SDRAM to operate in a more complex fashion and at much higher speeds than an asynchronous DRAM.

#### Single Data Rate (SDR) SDRAM

Also simply known as SDRAM, it transmits data (read/write) on only one clock transition, typically on the clock's rising edge, hence the name single data rate. To perform another operation, it has to wait for the previous one to be completed, making it slower than succeeding SDRAM generations.

| 44 |           |                | 9.51.9Witte | THUR DE LE | <br>11111111111111 |        |

|----|-----------|----------------|-------------|------------|--------------------|--------|

|    |           |                | ç ç         |            |                    | manuth |

| Ö  | di detado | n sing ting oc |             |            |                    | 6      |

ATP SDRAM module

Double Data Rate (DDR) SDRAM

Also simply known as DDR, it achieves greater bandwidth and faster performance at twice the speed of SDR by transferring data on both the rising and falling edges of a clock cycle.

DDR generations, which will be discussed in succeeding sections, include:

- DDR1

- DDR2

- DDR3

- DDR4

- DDR5

## ATP Legacy SDRAM Specifications

**Synchronous Dynamic Random-Access Memory (SDRAM)** refers to memory that operates synchronously with the system clock. The synchronous interface enables the SDRAM to operate in a more complex fashion and at much higher speeds than an asynchronous DRAM.

Please refer to motherboard/CPU/chipset documentation for memory requirements and compatibility.

# ATP Legacy DDR1 Specifications

| DDR1                       |               |                             |  |  |  |  |

|----------------------------|---------------|-----------------------------|--|--|--|--|

| DIMM Type                  | Non-ECC UDIMM | Non-ECC SO-DIMM             |  |  |  |  |

| Density                    | 256 MB        | 128 MB to 512 MB / 1 GB     |  |  |  |  |

| Speed up to (MT/s)         | 400           | 400                         |  |  |  |  |

| PCB Height                 | Low Profile   | Low Profile                 |  |  |  |  |

| Operating Temperature (Ta) | 0°C to 70°C   | 0°C to 70°C / -40°C to 85°C |  |  |  |  |

Please refer to motherboard/CPU/chipset documentation for memory requirements and compatibility.

| erii or | a dha | <b>De</b> Êeo | 6994V-8 (1999) | 1229 File |  |

|---------|-------|---------------|----------------|-----------|--|

## ATP Legacy DDR2 Specifications

|                            | D                           | DR2                         |          |

|----------------------------|-----------------------------|-----------------------------|----------|

| DIMM Type                  | ECC UDIMM                   | Non-ECC UDIMM               | No       |

| Density                    | 1 GB to 2 GB                | 1 GB to 2 GB                | 256      |

| Speed up to (MT/s)         | 800                         | 800                         |          |

| PCB Height                 | Low Profile                 | Low Profile                 |          |

| Operating Temperature (Ta) | 0°C to 85°C / -40°C to 85°C | 0°C to 85°C / -40°C to 85°C | 0°C to 8 |

Please refer to motherboard/CPU/chipset documentation for memory requirements and compatibility.

Ion-ECC SO-DIMM

6 MB / 1 GB to 4 GB

800

Low Profile

85°C / -40°C to 85°C

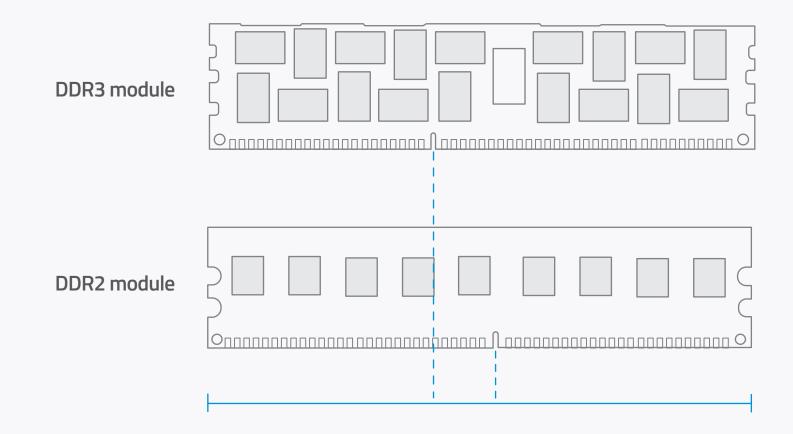

### DDR3

DDR3 operates at 1.5V (normal) and 1.35V (low voltage), consuming less power than its predecessors, and delivers better performance with a transfer speed of up to 1866 MT/s.

A DDR3 module is not pin-compatible with prior-generation modules and its alignment key is located differently to prevent being inserted into incompatible slots.

# ATP DDR3 Specifications

| DDR3                       |                                |                                |                                |                                |                                |                                |                                |

|----------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| DIMM Type                  | RDIMM                          | ECC UDIMM                      | Non-ECC UDIMM                  | ECC SO-DIMM                    | Non-ECC SO-DIMM                | Mini-RDIMM                     | Mini-UDIMM                     |

| Density                    | 1 GB to 32 GB                  | 1 GB to 16 GB                  |

| Speed up to (MT/s)         | 1866                           | 1866                           | 1866                           | 1866                           | 1866                           | 1600                           | 1600                           |

| PCB Height*                | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     | Low Profile                    | Low Profile                    | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     |

| Operating Temperature (Ta) | 0°C to 85°C /<br>-40°C to 85°C |

\* VLP: 0.74", ULP: below 0.74"

Please refer to motherboard/CPU/chipset documentation for memory requirements and compatibility.

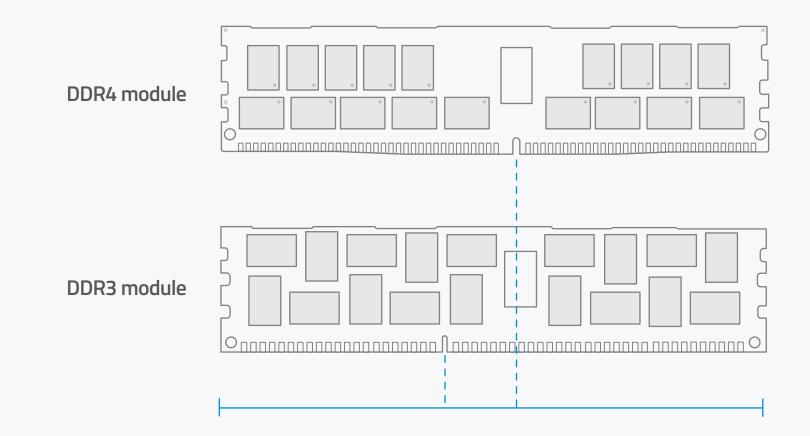

### DDR4

DDR4 is the evolutionary transition from DDR3. It consumes a mere 1.2V while performing up to 3200 MT/s data transfer rate to deliver faster performance while generating more power savings over earlier DRAM technologies.

A DDR4 module has 288 pins (260 pins for SO-DIMMs) and is not pin-compatible with prior-generation modules. The edge connector looks like a slightly curved "V" to facilitate insertion. This design also lowers insertion force, as not all pins are engaged at the same time during module insertion. Its alignment key is located differently to prevent being inserted into incompatible slots.

## ATP DDR4 Specifications

| DDR4                          |                                |                                |                                |                                |                                |                                |                                |

|-------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| DIMM Type                     | RDIMM                          | ECC UDIMM                      | Non-ECC UDIMM                  | ECC SO-DIMM                    | Non-ECC SO-DIMM                | Mini-RDIMM                     | Mini-UDIMM                     |

| Density                       | 4 GB to 128 GB                 | 4 GB to 32 GB                  | 2 GB to 32 GB                  | 4 GB to 32 GB                  | 2 GB to 32 GB                  | 4 GB to 16 GB                  | 4 GB to 16 GB                  |

| Speed up to<br>(MT/s)         | 3200                           | 3200                           | 3200                           | 3200                           | 3200                           | 2400                           | 2400                           |

| PCB Height*                   | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     | Low Profile                    | Low Profile                    | Low profile /<br>VLP / ULP     | Low profile /<br>VLP / ULP     |

| Operating<br>Temperature (Ta) | 0°C to 85°C /<br>-40°C to 85°C |

\* VLP: 0.74", ULP: below 0.74"

Please refer to motherboard/CPU/chipset documentation for memory requirements and compatibility.

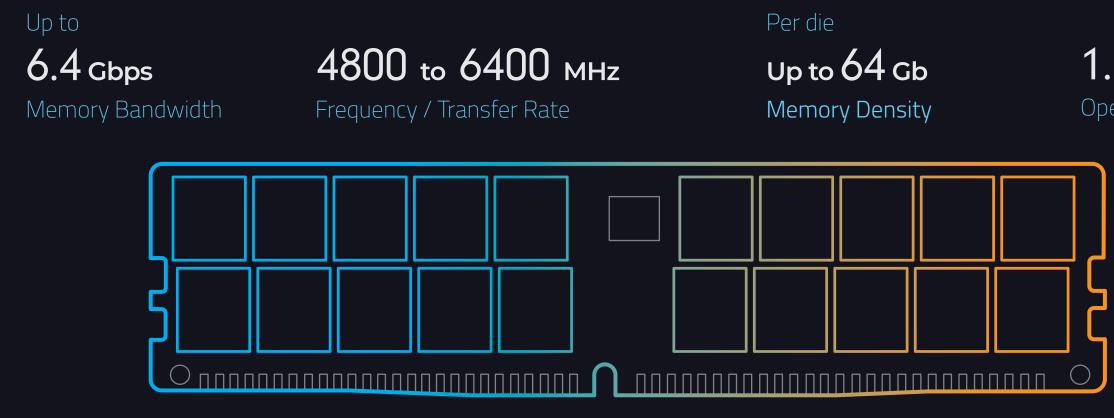

### DDR5

DDR5 is the next-generation DRAM specification. It is poised to exceed DDR4 in every way. DDR5 promises faster performance, higher memory bandwidth, higher densities, and a new power management structure that delivers better power efficiency. All of these advantages, and more, are expected to meet the ever-growing memory needs of present and future applications.

Both DDR4 and DDR5 dual-inline memory modules (DIMMs) still have 288 pins, but with DDR5's higher bandwidth, this means it can transmit data faster. While the pin count is the same, DDR5 DIMMs will not fit in DDR4 sockets as the alignment key is located differently and the pinouts have been changed to accommodate the new features.

## DDR5 Advantages Over DDR4

### Memory Bandwidth

This refers to the theoretical maximum amount of data that can be transmitted (read/written) within a given time. Memory bandwidth is expressed in gigabits per second (Gbps). DDR5 memory bandwidth is initially at 4.8 Gbps per pin, compared with DDR4's 3.2 Gbps. Future versions are expected to double DDR4's, going up to a maximum of 6.4 Gbps.

### Frequency / Transfer Rate

Memory frequency refers to the number of commands or transfer operations that the memory module can handle per second. It is typically expressed in megahertz (MHz), but some manufacturers use express this in mega transfers per second (MT/s). The number follows the DDR version, so a DDR5-4800 DIMM, for example, has a frequency of 4800 MHz (or 4800 MT/s).

DDR4 frequency ranges from 1866 to 3200 MHz, while DDR5 ranges from 4800 to 6400 MHz initially, but may go as high as 8400 MHz.

#### Memory Density

DDR4 maximum density is 16 Gb per die, so with 16 die, this translates to 256 Gbit or a total of 32 GB. DDR5, in comparison, has 64 Gb per die, translating to 1024 Gbit or a total of 128 GB – this is 4X that of DDR4, enabling higher-capacity DIMMS!

### **Burst Length**

This is the amount of data, which is input/output based on a single read/write command in DRAM. DDR5 doubles DDR4 burst length from 8 to 16, thus increasing the read/write efficiency.

### Power Management and Consumption

The first power management IC (PMIC) on DIMM is introduced in DDR5. PMIC performs local voltage regulation on the module. Historically, voltage regulation has been done on the motherboard. PMIC on the module allows additional features such as threshold protection, error injection capabilities, programmable power-on sequence, and power management features (Source: Micron). DDR5's lower voltage of 1.1V compared with DDR4's 1.2V further reduces power consumption.

### DDR5 vs. DDR4

The following table summarizes important enhancements of DDR5 from DDR4.

|                            | DDR5              | DDR4              |

|----------------------------|-------------------|-------------------|

| VDD*                       | 1.1V              | 1.2V              |

| Data Rates                 | 4800 to 6400 MT/s | 1866 to 3200 MT/s |

| Component Density          | 16 Gb to 64 Gb    | 4 Gb to 16 Gb     |

| DQ Bus Width (NON-ECC/ECC) | 64/80 bits        | 64/72 bits        |

| On-Die ECC                 | Yes               | No                |

| Power Management           | On DIMM PMIC*     | On Motherboard    |

\* VDD: Stands for Voltage Drain Drain, which is the drain power voltage PMIC: Power Management Integrated Circuit

### DDR5 Market Situation

While many module houses started sampling 1st Gen. DDR5 to customers in 2021, the price gap at the functional level to justify the adoption for DDR5 over DDR4 is too wide to consider in ATP's view.

8 GB UDIMM

#### DDR5 Component

### Insider Tips on Time-to-Market for DDR5

DDR5 timeframe

• Price is key. Future die shrink and optimizer will lead to a better commercial situation for DDR5 adoption

| 2022                                                                                                                                                                                                                                      | 2023                                                                                                                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4800 Mbps                                                                                                                                                                                                                                 | 5600 Mbps                                                                                                                                                                     |  |

| <ul> <li>DDR5 ecosystem starts to build up:</li> <li>1<sup>st</sup> usage will be consumer applications</li> <li>CM/EMS start to develop relevant platforms to be on AVL</li> <li>Servers will release 1st Gen to support DDR5</li> </ul> | <ul> <li>Speed will be upgraded to 5600 MT/s.</li> <li>DDR5 will be the primary focus of NPIs.</li> <li>DDR5 is still premium but gap may minimize between 15-20%.</li> </ul> |  |

| DDR5 vs. DDR4 |       |  |  |  |

|---------------|-------|--|--|--|

| DDR4          | DDR5  |  |  |  |

| 1x            | 1.57x |  |  |  |

| 1x            | 1.7x  |  |  |  |

2024

6400 Mbps

Sweet spot for DDR5 products

# Summary: DRAM Generations

|                 |                  | Generation | Voltage      | Pin Count |

|-----------------|------------------|------------|--------------|-----------|

| TSOP II Package |                  | SDRAM      | 3.3V         | 168 pins  |

|                 |                  | DDR1       | 2.5V         | 184 pins  |

| BGA Package     | AJ28K72F88JE65 G | DDR2       | 1.8V         | 240 pins  |

|                 |                  | DDR3       | 1.5V / 1.35V | 240 pins  |

|                 |                  | DDR4       | 1.2V         | 288 pins  |

|                 |                  | DDR5       | 1.1V         | 288 pins  |

# Categories

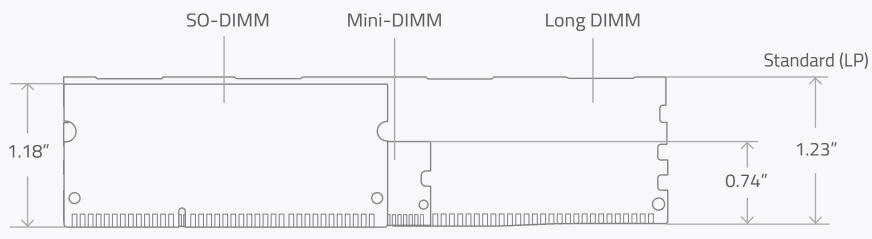

## Categories by Form Factor

Length

- Long DIMM

- SO-DIMM\*

- Mini-DIMM

Height

- Standard (LP): 1.18" to 1.23"

- VLP\*: 0.72" to 0.74"

- ULP\*: 0.7" to 0.72"

Form factor dimensions may vary depending on DRAM generation. The illustration below shows the height of different DDR4 form factors.

DDR4 DRAM heights by form factor

\* SO-DIMM: Small Outline Dual In-Line Memory Module VLP: Very Long Profile ULP: Ultra Low Profile

## Categories by Function

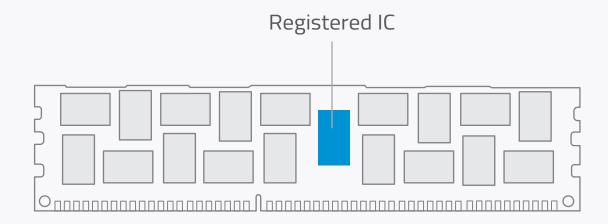

### RDIMM (Registered)

- Also known as "buffered" memory, RDIMMs feature onboard memory registers (hence the name "registered") placed between the memory and the system's memory controller.

- The register controls the amount of control and address signals that flow onto the module.

- The memory controller buffers Command, Addressing and Clock Cycling, directing instructions to the dedicated memory registers instead of accessing the DRAM directly. This reduces the electrical load on the memory controller.

### UDIMM (Unbuffered/Unregistered)

- Used mainly on consumer desktop and laptop computers, they run faster from the memory controller residing in the CPU to the memory module.

- The chipset of system drive directly controls and addresses signals into and memory chips.

and cost less but are not as stable as registered memory. Commands go directly

the memory chips of the module without any logical chips between chipset

## **Categories by Function**

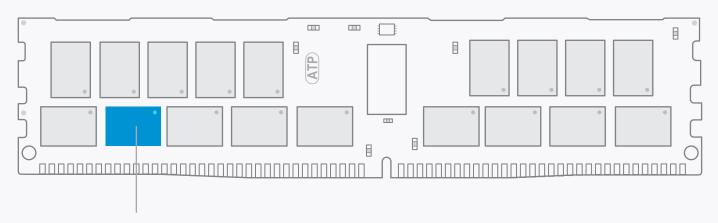

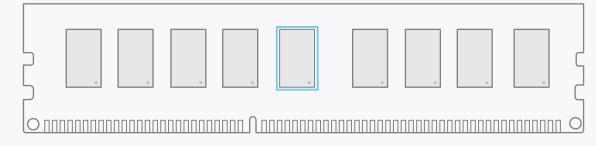

### Error Correction Code (ECC) DIMM

- An ECC memory module has an additional memory chip to detect and correct errors.

- ECC DIMMs typically have 9 or 18 memory chips to realize a module data width of 72 bits.

### Non-ECC DIMM

Non-ECC modules have either 8 or 16 DRAM components to realize a module data width of 64 bits.

ECC UDIMM

ECC SO-DIMM

#### Non-ECC UDIMM

Non-ECC SO-DIMM

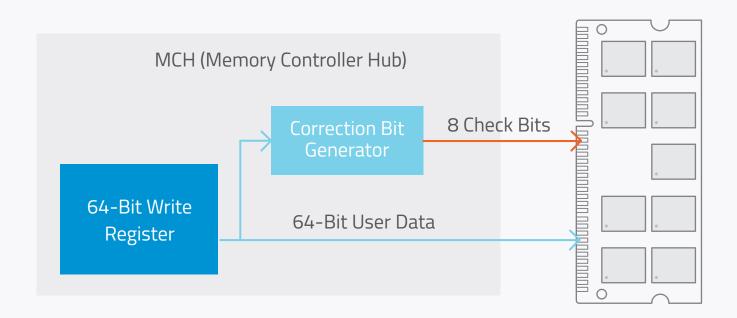

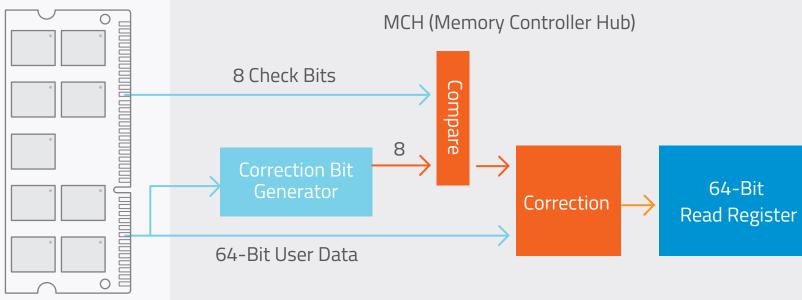

### Implementation of ECC Writes

- The error correction is performed in the MCH (Memory Controller Hub) alone.

- The DRAM module has a data width of 72 bits and all ECC codes will not modify the 64-bit user data.

- The correction bit generator will create 8 check bits by computing different checksums out of the 64 bits.

- The 64-bit user data and 8 check bits are written in parallel into the module.

### Implementation of ECC Reads

- A read from the module provides 72-bit data, 64-bit user data and 8 check bits

- The correction bit generator creates a "new" set of 8 check bits.

- The read check bits and a new set are compared

- If equal  $\rightarrow$  no failure

- If not equal  $\rightarrow$  bit error

- Comparison results indicate wrong bit position

- Inversion unit fixes the wrong bit and correct data is transferred to the read register

Module Organization and Capacity

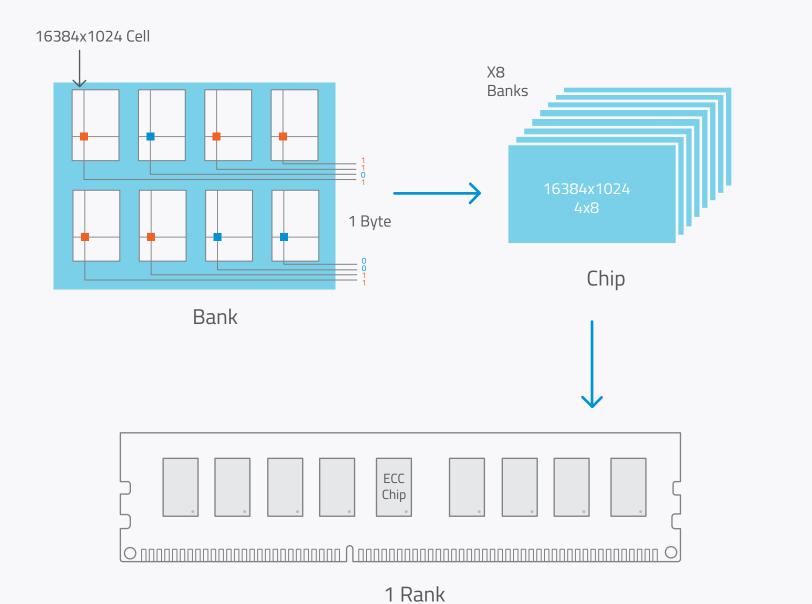

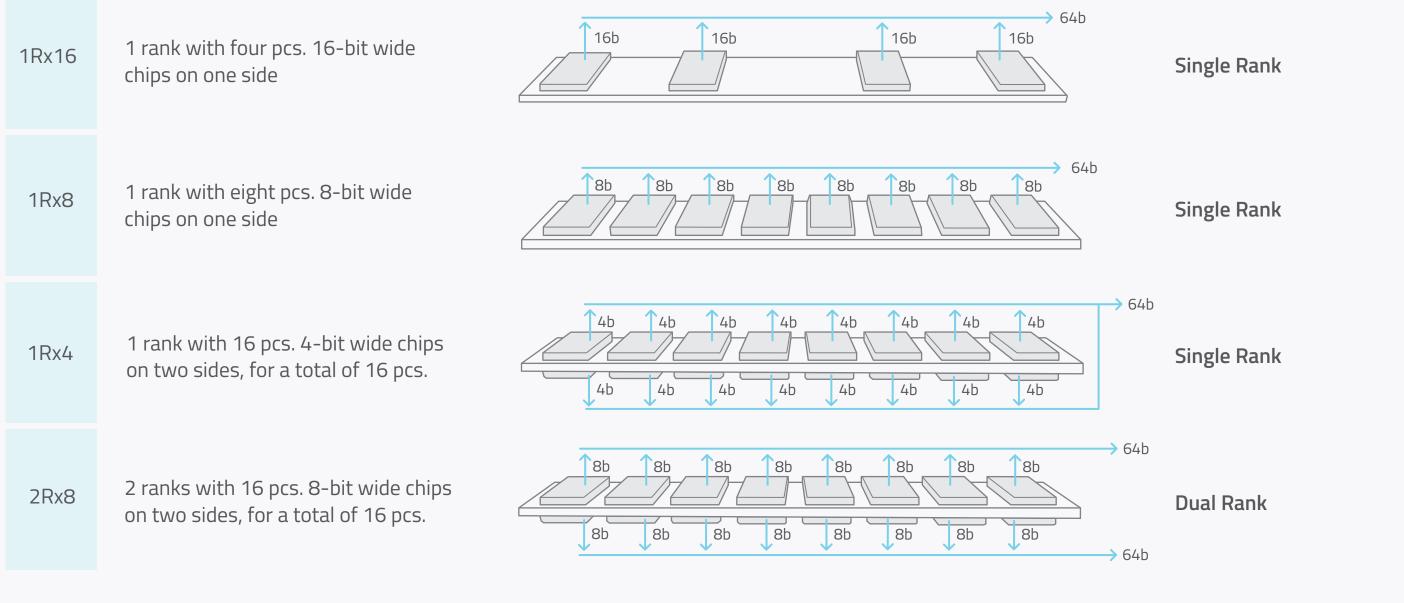

## Side/Rank/SPD

Bank

- A set of memory arrays is called a Bank.

- Data width of a Bank: 4/8/16 bits

- Chip

- Only one bank can be accessed each time.  $\longrightarrow$  Chip data width = Bank data width

- Rank

- A set of chips forms a Rank. 1 Rank = 64-bit / 72-bit (ECC).

• Each rank works independently and has its own chip selection signal: CS. Following JEDEC standard, DDR4 can have 1, 2, or 4 ranks.

## Side/Rank/SPD

## Double-Sided

It is a physical term that means memory chips are located on two sides of the memory module.

#### Dual Rank

It is an electrical term that means the module is divided electrically into two memory ranks.

1 Rank = 64 bits (Non-ECC) / 72 bits (ECC)

The physical arrangement of the chips does not always indicate the rank. Single-sided modules may not always be a single rank, and dual-sided modules may not always be dual rank.

## Serial Presence Detect (SPD)

- manufacturer, serial number and other useful information about the module.

- E<sup>2</sup>PROM stands for "electrically erasable programmable read-only memory." It is a type of non-volatile memory that stores a small byte of stored data using electrical voltage.

SPD uses an E<sup>2</sup>PROM (also called EEPROM) to store information on the configuration of memory modules, such as timing parameters,

amount of data. It allows users to erase and reprogram an individual

## Chip Density and Configuration

Chip density refers to the amount of memory cells of an individual chip on the module. The following table shows typical chip densities and configurations.

| Chip Density & Configurations |             | Address Mapping | Data Width |  |

|-------------------------------|-------------|-----------------|------------|--|

|                               | 1024 Mb x 4 | 1024 Mb         | 4 bits     |  |

| 4 Gb                          | 512 Mb x 8  | 512 Mb          | 8 bits     |  |

|                               | 256 Mb x 16 | 256 Mb          | 16 bits    |  |

|                               |             |                 |            |  |

|                               | 2048 Mb x 4 | 2048 Mb         | 4 bits     |  |

| 8 Gb                          | 1024 Mb x 8 | 1024 Mb         | 8 bits     |  |

|                               | 512 Mb x 16 | 512 Mb          | 16 bits    |  |

|                               |             |                 |            |  |

| 16 Gb | 4096 Mb x 4 | 4096 Mb | 4 bits  |

|-------|-------------|---------|---------|

|       | 2048 Mb x 8 | 2048 Mb | 8 bits  |

|       | 1 Gb x 16   | 1024 Mb | 16 bits |

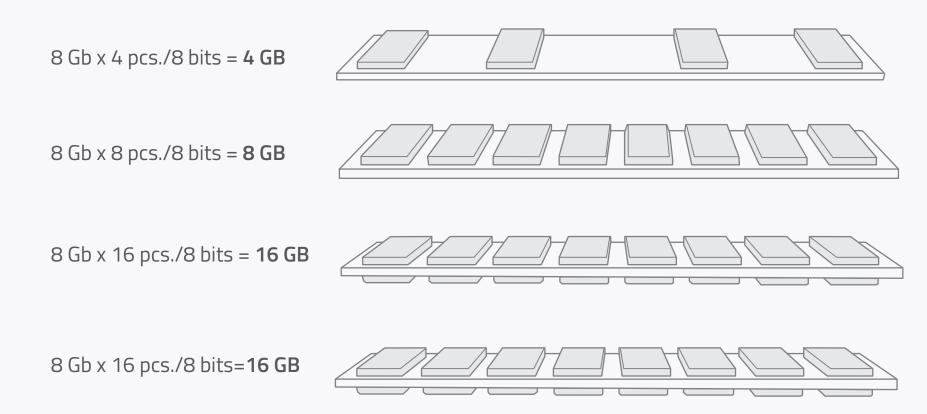

## Module Rank and Capacity Calculation

1 Rank = Data width of 64 bits (72 bits if with ECC)

## Capacity Calculation

How to compute module capacity

Sample IC/component capacity: 8 Gb

<u>Notes</u>: 1 GB\* = 8 Gb\* ECC ICs are not included in the capacity calculation

Formula: IC Capacity x Pcs. of IC / 8 bits = Module Capacity

\*GB: Gigabyte \*\*Gb: Gigabit

## Applications

Maximized utilization and quick scale-out performance

**Cloud**: High density, low power solutions improve TCO Micro Server: Low cost and reduced latency Embedded: Wide range of capacity options

42

## Chapter 2 ATP Differentiators

| 1. Industrial Quality          | 44 |

|--------------------------------|----|

| 2. Longevity Program           | 45 |

| 3. ATP DRAM Testing            | 48 |

| 3.1 Functional Testing: ATE    | 50 |

| 3.2 System Testing: ATP TDBI   | 50 |

| 4. Other Unique Features       |    |

| 4.1 Wide Temp Modules Solution | 54 |

| 4.2 Golden Fingers             | 55 |

| 1 3 Anti-Sulfur Posistors      | 55 |

5. Customization Services

5.1 Conformal Coating

5.2 Chamfering PCB Design

#### 6. ATP DRAM Products

56 56

57

## Industrial Quality

ATP is committed to providing the highest-quality DRAM modules suitable for rigorous industrial and embedded applications.

- Designed and manufactured with extensive screening & testing

- Best TCO value with longevity & higher endurance for industrial applications

- Full in-house process ownership for uncompromising quality guarantee

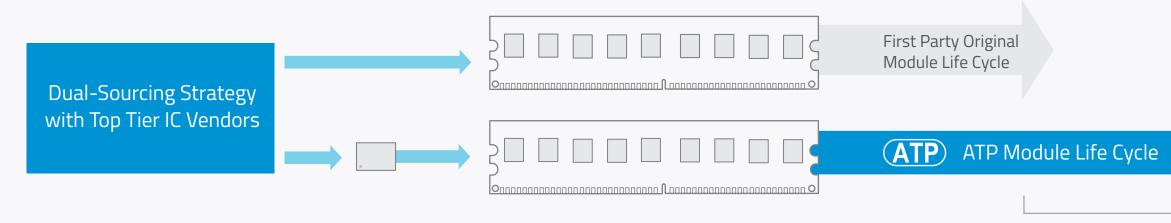

The ATP quality umbrella covers both mainstream original modules and second-source/legacy ATP-built modules.

#### Whole Project Life Cycle ATP QA + Traceability

- BOM Control, Label traceability

- ATP Quality/Testing Coverage

**Ongoing Longevity Support**

• Coverage of multiple DRAM suppliers and process nodes

## Longevity Program

Micron and ATP Partnership and License Agreements ensure legacy DDR2/DDR/SDR DRAM module supply.

### DDR2 Continuity Program

With DDR2 still widely deployed in the US, Japan and Europe, ATP and Micron are making sure that these markets will have a steady supply of Micron DDR2 SO-DIMMs and UDIMMs for industrial/embedded systems installed in high-reliability and mission-critical environments. All modules are manufactured, tested and validated by ATP, according to the equivalent specifications and testing/validation processes of the respective Micron part number.

| Module Type    | DDR2 UDIMM                             | DDR2 SO-DIMM                |

|----------------|----------------------------------------|-----------------------------|

| Capacity       | 1 GB / 2 GB                            | 256 MB / 1 GB / 2 GB / 4 GB |

| Function       | Unbuffered ECC /<br>Unbuffered Non-ECC | Unbuffered Non-ECC          |

| Frequency      | 800 MHz                                | 800 MHz                     |

| Number of Pins | 240                                    | 200                         |

| PCB Height     | 1.18"                                  | 1.18"                       |

## Longevity Program

## Legacy (SDR/DDR) DRAM Modules

Under a license agreement with Micron Technology, Inc. signed in August 2015, ATP will continue to manufacture legacy SDR/DDR DRAM modules for Micron's customers who are unable to migrate. The agreement was expanded in 2016 with the addition of selected legacy DRAM modules specifically for customers using AMD Embedded/Geode platforms. ATP works closely and exclusively with Micron to transfer module designs and extend long-term support to offer the legacy modules in selected form factors (SO-DIMM, UDIMM and RDIMM) and densities, along with ATP's unique services and features.

The license agreement stipulates the following conditions for ATP:

- IOO% follow Micron's design. Offer extended support for these legacy products to minimize the customer's (re)qualification efforts.

- IOO% follow Micron's BOM selection. Implement the same specifications for key components (such as IC configuration and Register/PLL type), as well as passive components (such as resistors, capacitors and EEPROM) to meet the specifications of Micron's BOM.

- 100% follow Micron's firmware settings. Implement SPD in addition to the manufacturer's information.

- 100% follow Micron's specifications. Each module will be manufactured to the equivalent specifications and test processes of the corresponding Micron part number.

## Longevity Program

#### **Product Information**

| Module Type                       | Capacity                           | Function           | Frequency | Number of Pins | PCB Height |

|-----------------------------------|------------------------------------|--------------------|-----------|----------------|------------|

| DDR SO-DIMM                       | 128 MB / 256 MB /<br>512 MB / 1 GB | Unbuffered Non-ECC | 400 MHz   | 200            | 1.25"      |

| DDR SO-DIMM<br>(Industrial Grade) | 256 MB / 512 MB                    | Unbuffered Non-ECC | 400 MHz   | 200            | 1.25"      |

| Build To Order (BTO) |                            |                    |           |                |              |  |  |  |

|----------------------|----------------------------|--------------------|-----------|----------------|--------------|--|--|--|

| Module Type          | Capacity                   | Function           | Frequency | Number of Pins | PCB Height   |  |  |  |

| DDR UDIMM            | 256 MB / 512 MB            | Unbuffered Non ECC | 400 MHz   | 184            | 1.25"        |  |  |  |

| SDRAM SO-DIMM        | 64 MB / 128 MB /<br>256 MB | Unbuffered Non ECC | 133 MHz   | 144            | 1.0" / 1.25" |  |  |  |

ATP DRAM modules undergo two levels of stringent Enhanced Module-Level Tests. Automatic Test Equipment (ATE) and system-level Test During Burn-In (TDBI) guarantee that modules meet and even exceed qualifying parameters.

| FUNCTIONAL/ATE TESTING                                                                                              | SYSTEM TESTING                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Detects structural and component defects</li> <li>Screens out marginal timings/SI sensitivities</li> </ul> | <ul> <li>100% System-level burn-in testing</li> <li>100% TDBI* accelerated burn-in testin<br/>Screens out weak ICs</li> </ul> |

\*Test During Burn-In. On a project basis; value-added service.

ting effectively

#### **FUNCTIONAL/ATE TESTING**

1. Automatic Test Equipment (ATE)

#### 2. Load SPD

#### TDBI: Testing During Burn In

- Industrial/Wide Temp (-40°C to 85°C):

- DDR2

- DDR3

- DDR4

#### SYSTEM TESTING

Room Temperature : SDRAM/DDR/DDR2/DDR3/DDR4

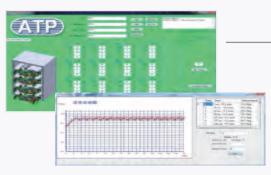

## Automatic Test Equipment (ATE)

The ATE detects component defects and structural defects related to the DIMM assembly and screens out marginal timing and signal integrity (SI) sensitivities. ATE provides electrical testing patterns with various parameter settings, such as marginal voltage, signal frequency, clock, command timing and data timing under continuous thermal cycle.

## Test During Burn-in (TDBI)

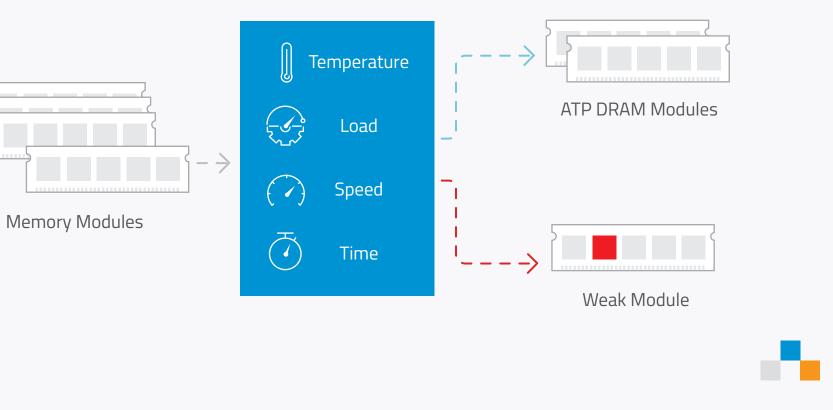

- TDBI at mass production level detects early life failures (ELF) and effectively screens out weak ICs that could fail during the early product life. It combines temperature, load, speed and time to stress test memory modules and expose the weak module.

- Even just 0.01% error on a 99.99% effective device can increase the failure rates at module level and lead to failure in actual usage.

- ATP TDBI can detect and screen out the 0.01% error to ensure utmost reliability.

#### ATP TDBI: What Makes It Unique?

The ATP TDBI system applies extreme high/low temperature, high-low voltage, and pattern testing on DRAM modules.

The system consists of:

#### The Mini Chamber

99

Isolates temperature cycling only to modules being tested so as not to thermally stress the rest of testing systems. This minimizes the failure of other testing components, such as the motherboards. It also allows faster debug for defects per million (DPM) fallout and reduced false failures. In conventional large thermal chambers, the failures of non-DRAM-related testing components are constant, given that the whole system is thermally stressed.

Module Riser Adapters from the Motherboard

Allow easy module insertions in production-level volumes.

### Improvements After TDBI Adoption

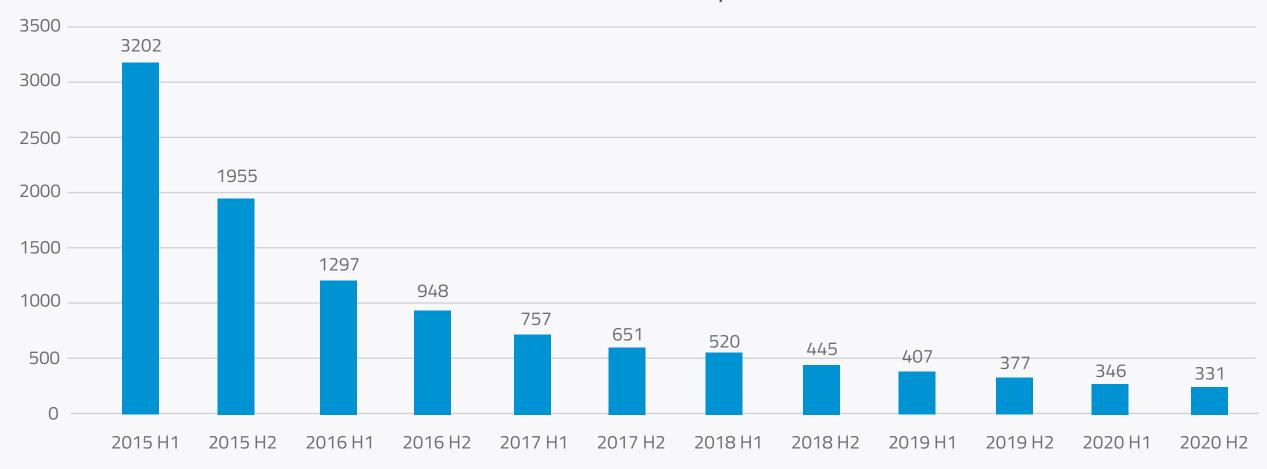

The following graph shows that with ATP TDBI, the error rates decrease over time. The acceptable industry limit is 3,500 DPPM,\* but with ATP TDBI, the error rate has gone down to just over 100 during the fourth year.

**DPPM\*** Summary

\*DPPM = Defective Parts per Million

ATP TDBI Equipment Overview

High/Low Temp Validation (-40°C to 85°C)

## 1 Cabinet carries 4 motherboards

#### Mini Chambers

## Other Unique Features

## Wide Temp DRAM Modules

Industrial grade modules can cost up to 2.5 times higher than commercial grade modules. ATP offers wide temperature modules, which can offer the best solution to reach industrial grade performance at a lower cost.

|                 | Commercial Grade<br>Modules | Wide Temperature<br>Modules                         | Industrial Grade<br>Modules |

|-----------------|-----------------------------|-----------------------------------------------------|-----------------------------|

| Target Market   | General DRAM Product        | Price Issue with IG Solution                        | Customer-Specified          |

| DRAM IC         | Major IC                    | Wide Temp IC                                        | Native IG* IC               |

| Operating Temp  | 0°C to 85°C                 | -40°C to 85°C                                       | -40°C to 85°C               |

| Testing Feature | ATE & Module Level TDBI     | ATE & Module Level Enhanced<br>TDBI (-40°C to 85°C) | ATE & Module Level TDBI     |

| Cost            | 1x\$                        | \$CG* < \$WT* DRAM < \$IG*                          | 2.5 X \$                    |

\*WT: Wide Temperature IG: Industrial Grade CG: Commercial Grade

## Other Unique Features

#### 30µ" Golden-Plated Connector

In order to achieve the best durability, all ATP DRAM modules comply with IPC-A-610 and adopt a 30µ (micro-inch) golden-plated connector to ensure stability under any tough environment.

The 30µ"-thick gold plating of the DRAM contact optimizes signal transmission quality between the connector and the DRAM module.

#### Anti-Sulfur Resistors\*

Ordinary silver resistors corrode and become non-conductive when exposed to sulfur. ATP DRAM modules products offer an anti-sulfur resistor option to prevent the corrosive effects of sulfur contamination, guaranteeing continued dependable performance for a long time and lowering the total cost of ownership by preventing unnecessary downtime and expensive component replacements.

\* Value-added feature, by project support.

## Customization Services

Depending on customer request, ATP offers optional value-added services.

Dust, chemical contaminants, extreme temperatures and moisture, corrosion may lead to DRAM short circuiting and malfunction.

ATP uses conformal coating to protect against contaminants and increase the DRAM modules' service life. ATP's conformal coating solution uses parylene coating technology via chemical vapor deposition (CVD). The coating material, which is compliant with US Military Material MIL-I-46058C and Fire Safety UL94V-0 Certification standards, is placed in a vacuum chamber. Inside the chamber, the coating material is directly vaporized and pyrolyzed into nano-molecular streams. It is then entered into a room-temperature coating chamber to gradually form an even and homogeneous protective film onto the profile of the DRAM module circuit assembly. The coating completely penetrates spaces as narrow as 0.01 mm, making it totally pinhole-free and truly conformal to shield the DRAM module from dust, chemicals, moisture, and other harmful substances.

Chamfering PCB Design

Chamfering refers to the process of "beveling or tapering" the connector edges for easier insertion into the memory slots. The bevel is done at specific angles, typically at around 40° to 50°.

# ATP DRAM Products

## Complete DRAM Portfolio

| Product | DIMM Type       | Capacity       | Speed<br>(MT/s, up to) | VLP/ULP* | 30µ″ Golden<br>Finger | ATP TDBI | Wide<br>Temperature | Anti-Sulfur<br>Resistors | Conformal<br>Coating | PCB Chamfer |

|---------|-----------------|----------------|------------------------|----------|-----------------------|----------|---------------------|--------------------------|----------------------|-------------|

|         | RDIMM           | 4 GB to 128 GB | 3200                   | •        | •                     | ٠        |                     |                          | -                    |             |

|         | ECC UDIMM       | 4 GB to 32 GB  | 3200                   | •        | •                     | •        |                     |                          |                      |             |

|         | Non-ECC UDIMM   | 2 GB to 32 GB  | 3200                   | •        | •                     | •        |                     |                          |                      |             |

| DDR4    | ECC SO-DIMM     | 4 GB to 32 GB  | 3200                   | -        | •                     | ٠        |                     |                          |                      |             |

|         | Non-ECC SO-DIMM | 2 GB to 32 GB  | 3200                   | -        | •                     | ٠        |                     |                          |                      |             |

|         | Mini-RDIMM      | 4 GB to 16 GB  | 2400                   | ٠        | •                     | •        |                     |                          | -                    | -           |

|         | Mini-UDIMM      | 4 GB to 16 GB  | 2400                   | •        | •                     | ٠        |                     |                          | _                    | _           |

▲ : Optional

\* VLP : height = 0.74"

ULP : height below 0.74"

## Complete DRAM Portfolio

| Product | DIMM Type       | Capacity      | Speed<br>(MT/s, up to) | VLP/ULP* | 30µ" Golden<br>Finger | ATP TDBI | Wide<br>Temperature | Anti-Sulfur<br>Resistors | Conformal<br>Coating | PCB Chamfer |

|---------|-----------------|---------------|------------------------|----------|-----------------------|----------|---------------------|--------------------------|----------------------|-------------|

|         | RDIMM           | 1 GB to 32 GB | 1866                   | •        | •                     | •        |                     |                          | -                    |             |

|         | ECC UDIMM       | 1 GB to 16 GB | 1866                   | •        | •                     | •        |                     |                          |                      |             |

|         | Non-ECC UDIMM   | 1 GB to 16 GB | 1866                   | •        | •                     | •        |                     |                          |                      |             |

| DDR3    | ECC SO-DIMM     | 1 GB to 16 GB | 1866                   | -        | •                     | ٠        |                     |                          |                      |             |

|         | Non-ECC SO-DIMM | 1 GB to 16 GB | 1866                   | -        | •                     | •        |                     |                          |                      |             |

|         | Mini-RDIMM      | 1 GB to 16 GB | 1600                   | •        | •                     | •        |                     |                          | -                    | _           |

|         | Mini-UDIMM      | 1 GB to 16 GB | 1600                   | •        | •                     | ٠        |                     |                          | -                    | _           |

▲: Optional

\* VLP: height = 0.74"

ULP: height below 0.74"

## Complete DRAM Portfolio

| Product | DIMM Type       | Capacity                   | Speed<br>(MT/s, up to) | VLP/ULP* | 30µ″ Golden<br>Finger | ATP TDBI | Wide<br>Temperature | Anti-Sulfur<br>Resistors | Conformal<br>Coating | PCB Chamfer |

|---------|-----------------|----------------------------|------------------------|----------|-----------------------|----------|---------------------|--------------------------|----------------------|-------------|

|         | ECC UDIMM       | 1 GB to 2 GB               | 800                    | -        | •                     | ٠        |                     | -                        | -                    | -           |

| DDR2    | Non-ECC UDIMM   | 1 GB to 2 GB               | 800                    | -        | •                     | ٠        |                     | -                        | -                    | -           |

|         | Non-ECC SO-DIMM | 256 MB /<br>1 GB to 4 GB   | 800                    | -        | •                     | •        |                     | -                        | -                    | -           |

|         | Non-ECC UDIMM   | 256 MB                     | 400                    | -        | •                     | ٠        | -                   | -                        | -                    | -           |

| DDR1    | Non-ECC SO-DIMM | 128 MB to 512 MB /<br>1 GB | 400                    | -        | •                     | ٠        |                     | -                        | -                    | _           |

| SDRAM   | Non-ECC SO-DIMM | 64 MB to 256 MB            | PC 133                 | -        | •                     | ٠        | -                   | -                        | _                    | -           |

▲ : Optional

\* VLP : height = 0.74"

ULP : height below 0.74"

## Ordering Information

|         | Hot Items Ordering Information |                        |       |        |        |  |  |  |  |  |  |

|---------|--------------------------------|------------------------|-------|--------|--------|--|--|--|--|--|--|

| Product | DIMM Type                      | Speed<br>(MT/s, up to) | SIZE  | CHIP   | HEIGHT |  |  |  |  |  |  |

|         | Unbuffered Non ECC UDIMM       | 1600                   | 4 GB  | 512x8  | 1.18"  |  |  |  |  |  |  |

| DDR3    | Unbuffered Non ECC UDIMM       | 1600                   | 8 GB  | 512x8  | 1.18"  |  |  |  |  |  |  |

|         | Unbuffered Non ECC SO-DIMM     | 1600                   | 4 GB  | 512x8  | 1.18"  |  |  |  |  |  |  |

|         | Unbuffered Non ECC SO-DIMM     | 1600                   | 8 GB  | 512x8  | 1.18"  |  |  |  |  |  |  |

|         | Hot Items Ordering Information |                        |       |        |        |  |  |  |  |  |  |

| Product | DIMM Type                      | Speed<br>(MT/s, up to) | SIZE  | CHIP   | HEIGHT |  |  |  |  |  |  |

|         |                                | 3200                   | 4 GB  | 512x16 | 1.18"  |  |  |  |  |  |  |

|         | Unb/Non ECC SO-DIMM            | 3200                   | 8 GB  | 1Gx16  | 1.18"  |  |  |  |  |  |  |

|         | SHB/NON LEC SO DIMIN           | 3200                   | 16 GB | 2GX8   | 1.18"  |  |  |  |  |  |  |

|         |                                | 3200                   | 32 GB | 2GX8   | 1.18"  |  |  |  |  |  |  |

| DDR4    |                                | 2666                   | 4 GB  | 512x16 | 1.18"  |  |  |  |  |  |  |

|         | Unb/Non ECC SO-DIMM            | 2666                   | 8 GB  | 1Gx16  | 1.18"  |  |  |  |  |  |  |

|         |                                | 2666                   | 16 GB | 2GX8   | 1.18"  |  |  |  |  |  |  |

|         |                                | 2666                   | 32 GB | 2GX8   | 1.18"  |  |  |  |  |  |  |

| Ranks | P/N            |

|-------|----------------|

| 1     | AQ12P64A8BLKOM |

| 2     | AQ24P64B8BLKOM |

| 1     | AW12P6438BLK0M |

| 2     | AW24P64F8BLK0M |

| Ranks | P/N            |

|-------|----------------|

| 1     | A4G04QC6BNWE*O |

| 1     | A4G08QC6BVWE*O |

| 1     | A4G16QA8BVWE*O |

| 2     | A4G32QE8BVWE*O |

| 1     | A4G04QC6BNTD*O |

| 1     | A4G08QC6BVTD*O |

| 1     | A4G16QA8BVTD*O |

| 2     | A4G32QE8BVTD*O |

\* M= Micron-based module, S= Samsung-based module

#### Follow us on

ATP Website

#### ATP TAIWAN

Headquarters

TEL: +886-2-2659-6368 sales-apac@atpinc.com

**ATP USA**

#### ATP EUROPE

#### ATP JAPAN

TEL: +1-408-732-5000 sales@atpinc.com

TEL: +49-89-374-9999-0 sales-europe@atpinc.com TEL: +81-3-6260-0797 sales-japan@atpinc.com

TEL: +86-21-5080-2220 sales@cn.atpinc.com

#### V1.0 2021

Copyright ©2021 , ATP Electronics Taiwan Inc. All rights reserved